Semi-parallel SC decoder implementation method and system based on FPGA

An implementation method and a decoder technology, which are applied in the field of FPGA-based semi-parallel SC decoder implementation methods and systems, can solve the problem of difficult decoder generation, increase the structural complexity of the semi-parallel SC decoder, and increase a small amount of decoding. code delay and other problems to achieve the effect of optimizing the structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. For the step numbers in the following embodiments, it is only set for the convenience of illustration and description, and the order between the steps is not limited in any way. The execution order of each step in the embodiments can be adapted according to the understanding of those skilled in the art sexual adjustment.

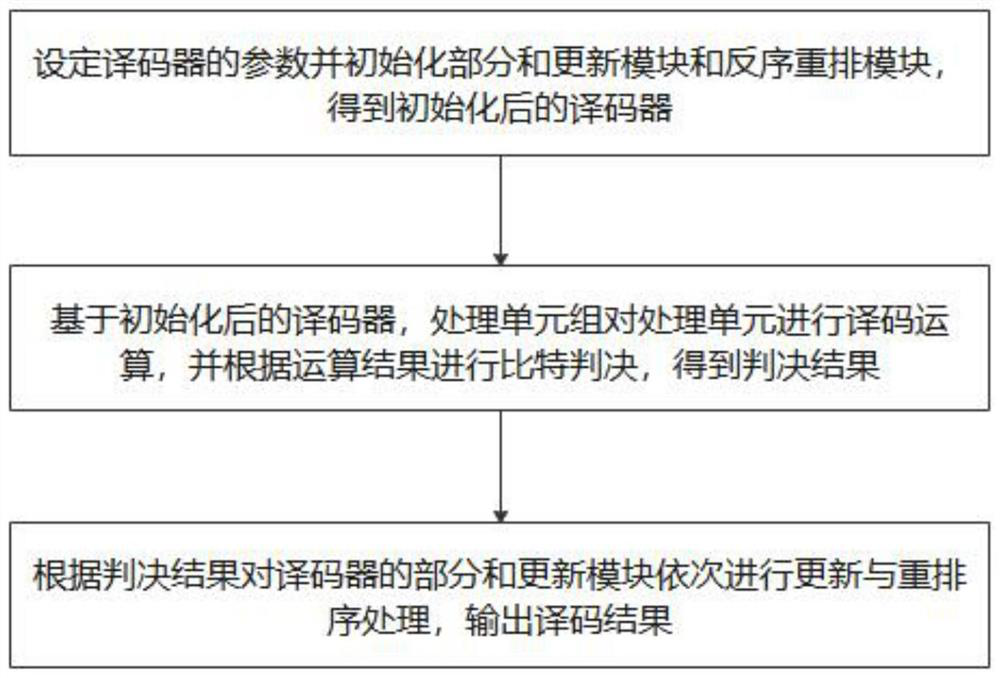

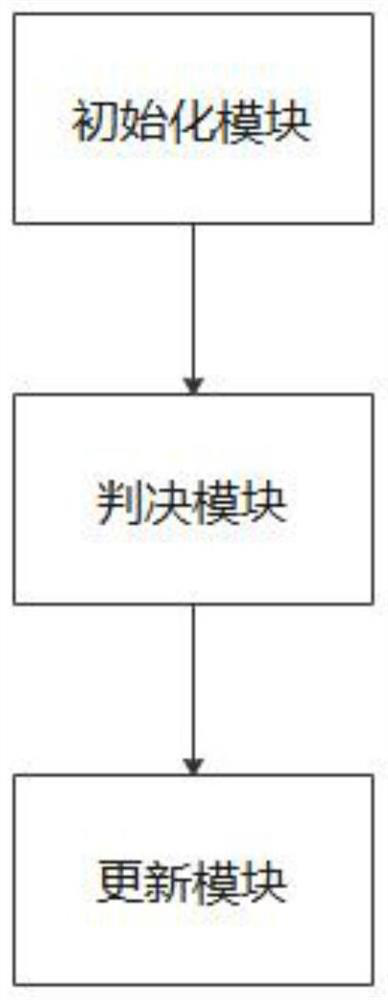

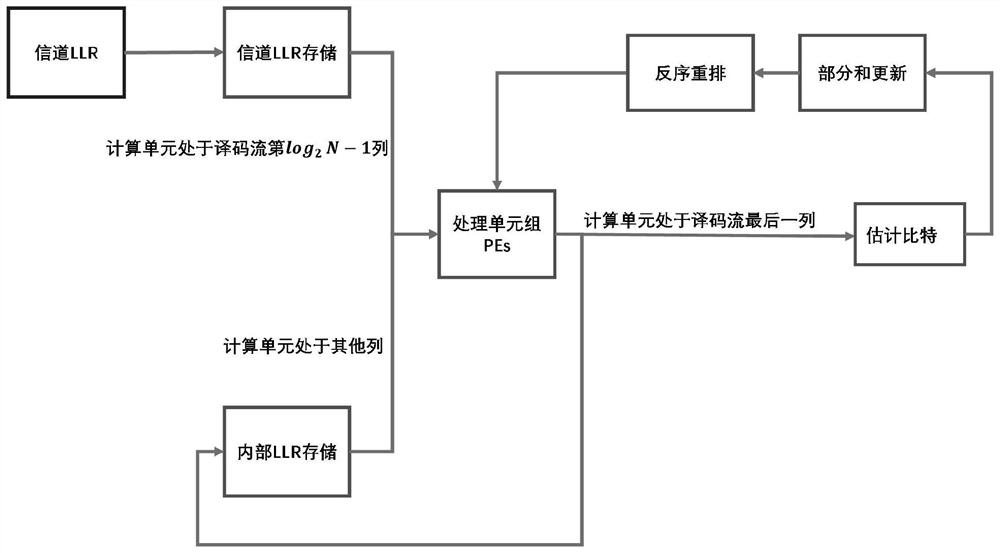

[0054] refer to figure 1 , the present invention provides a kind of semi-parallel SC decoder implementation method based on FPGA, and this method comprises the following steps:

[0055] S1. Setting the parameters of the decoder and initializing the part and update module and the reverse sequence rearrangement module to obtain the initialized decoder;

[0056] S11. Set the parameters of the decoder, and set the fixed-point scheme of the system. The parameters of the decoder include the code length of the polar code t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com