Differential input voltage charge scaling SARADC

A differential input and scaling technology, which is applied in electrical components, signal transmission systems, electrical signal transmission systems, etc., can solve the problem of inability to meet the design requirements of multi-bit high-speed and high-bandwidth ADCs, weak anti-interference ability of single-ended analog signal input, layout problems, etc. Problems such as inability to be highly matched can achieve the effect of improving linear performance, achieving high matching, and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

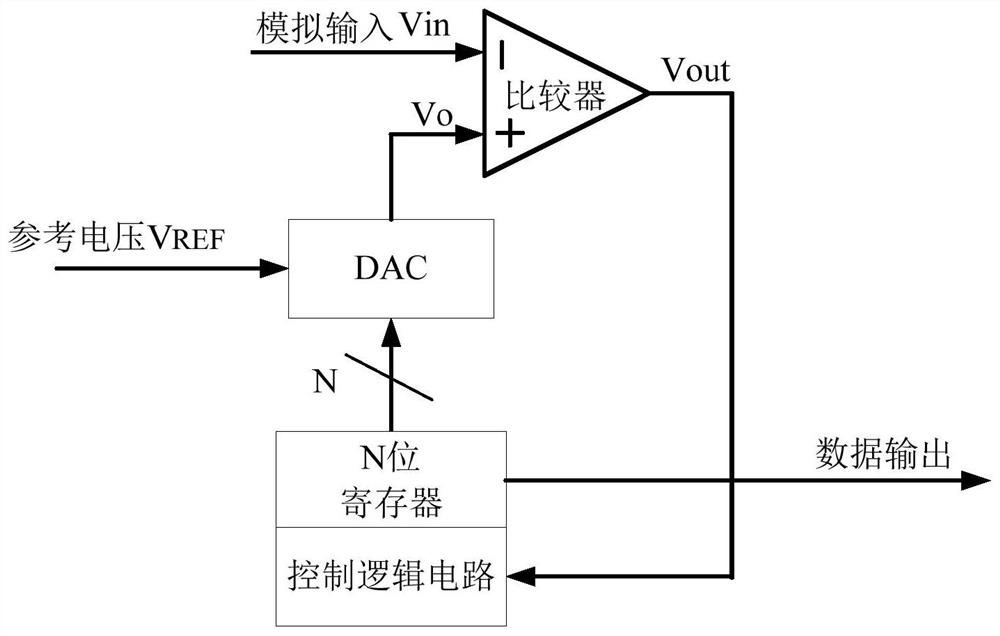

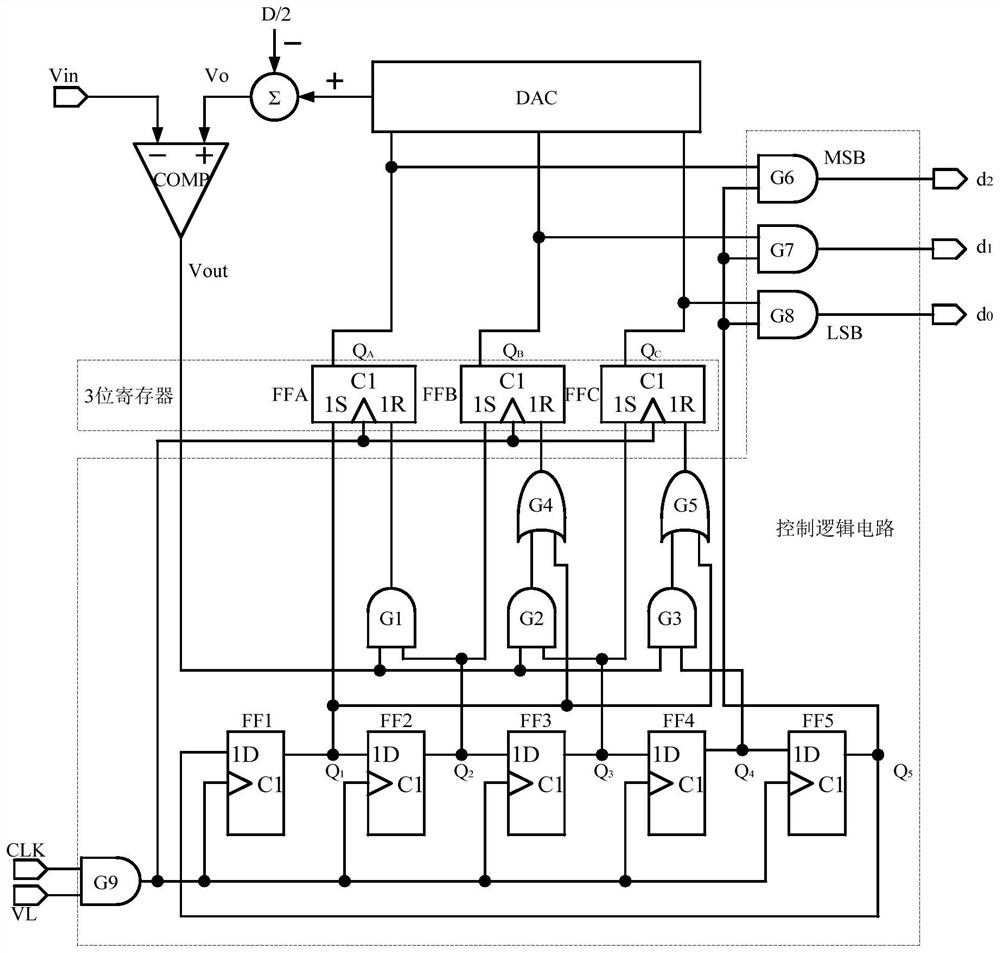

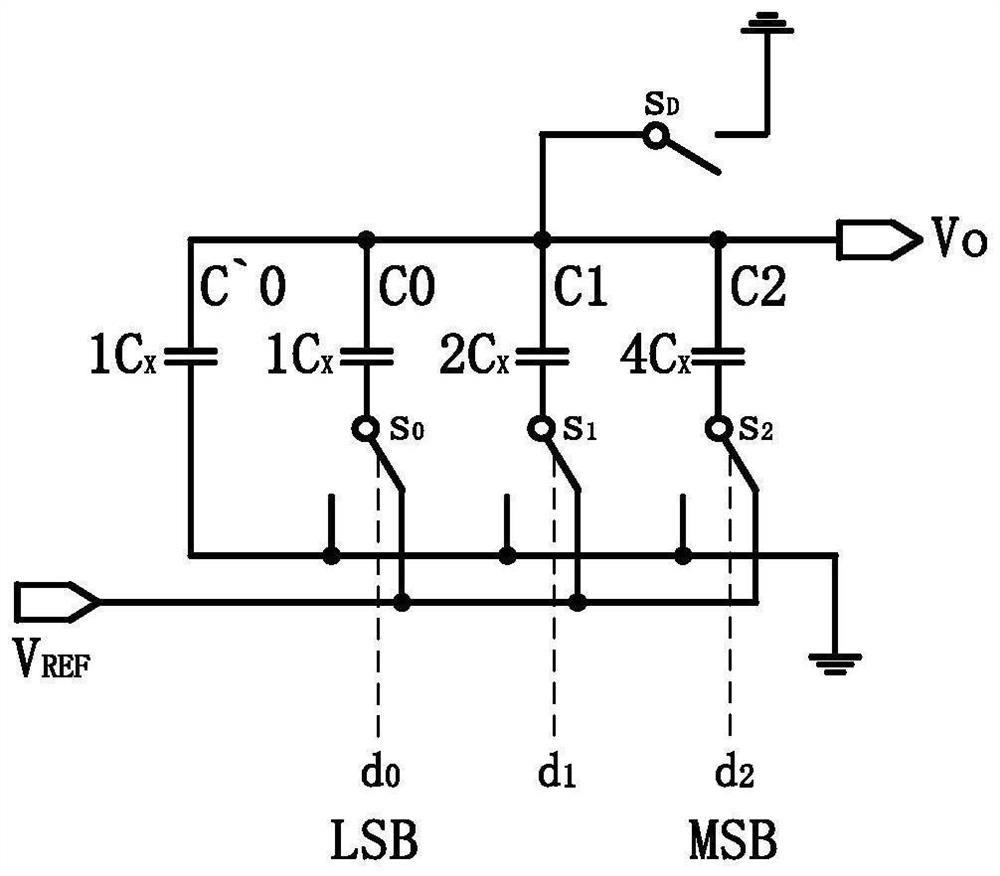

[0086] Specific embodiment one: the following combination Figure 4 to Figure 15 This embodiment is described. A differential input voltage charge scaling SAR_ADC described in this embodiment includes a VREF voltage divider, a capacitor array DAC1, a capacitor array DAC2, a comparator, a SAR logic circuit and an N-bit register; a capacitor array DAC1 and a capacitor The array DAC2 adopts A+B bit combination DAC, the high A part is capacitive scaling, the low B part is the reference voltage scaling, N=A+B;

[0087] VREF voltage divider provides voltage for capacitor array DAC1 and capacitor array DAC2;

[0088] The capacitor array DAC1 and the capacitor array DAC2 are connected to the differential input signals VREF-AD and AD, where VREF is the system reference voltage and AD is the analog input signal;

[0089] The capacitor array DAC1 and the capacitor array DAC2 each output N voltage values under the control of the SAR logic circuit. Each time the output voltages...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com