Design method of three-dimensional network-on-chip topological structure

An on-chip network and topology technology, applied in computing, computers, computing models, etc., can solve problems such as poor optimization results, low efficiency, and inability to intelligently design space exploration, etc., to achieve good optimization results, high search efficiency, and optimal search The effect of the result

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

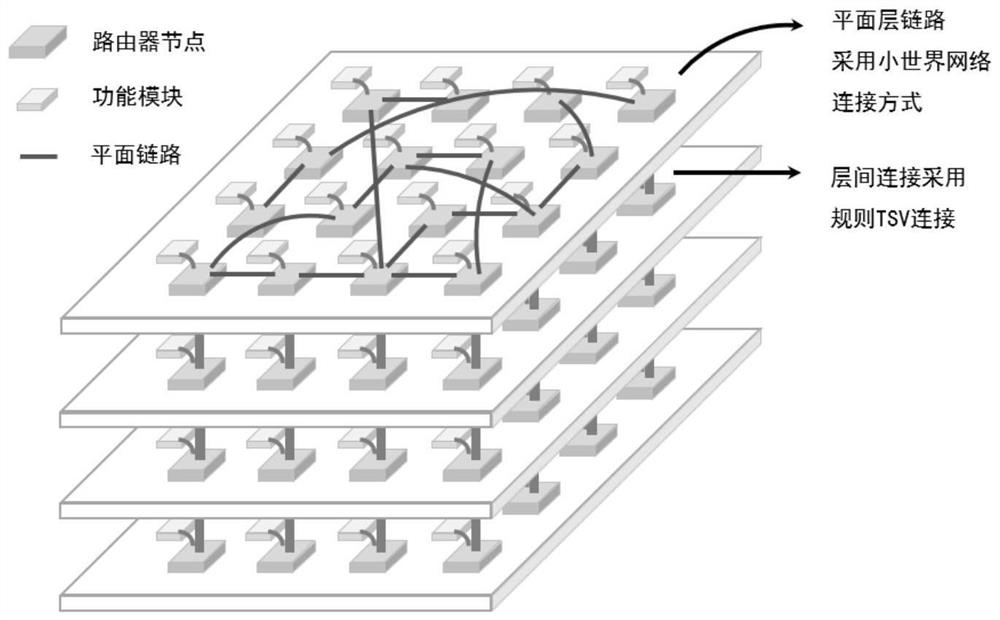

[0066] The specific implementation of the present invention will be further described below by taking the generation of a 4x4x4 three-dimensional network-on-chip topology structure as an example in conjunction with the accompanying drawings, but the implementation and protection of the present invention are not limited thereto.

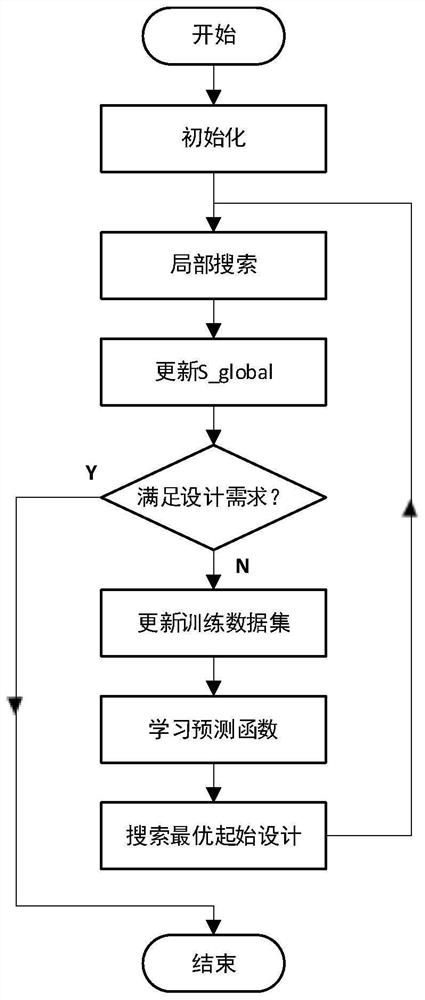

[0067] Such as figure 1 , the specific implementation steps of the present invention are as follows: Step 1, the designer determines the network scale parameters and target application traffic characteristics; Step 2, initialization; Step 3, local search; Step 4, global search; Step 5, cyclic execution of steps 3 and 4 , until a solution that meets the design requirements is generated, and a low-latency, high-throughput 3D SWNoC topology is obtained; steps 1 to 4 are described in detail below.

[0068] Step 1, the designer determines the network scale parameters and target application traffic characteristics

[0069] For the 4x4x4 three-dimensional o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com