On-chip power consumption management method, electronic device and storage medium

A power consumption management method and power consumption technology, which is applied in data processing power supply, electrical digital data processing, measurement flow/mass flow, etc., can solve problems such as abnormal chip operation, achieve control of chip abnormality, improve chip power supply integrity, The effect of active power control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

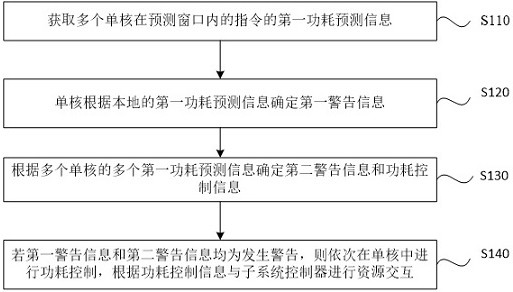

[0023] figure 2 The flow chart of the on-chip power consumption management method provided by Embodiment 1 of the present invention, this embodiment is applicable to the situation of controlling chip power consumption, this method can be executed by electronic equipment with large-scale integrated circuits, and the electronic equipment can For smart terminals, personal computers, tablet computers or notebook computers, etc., specifically include the following steps:

[0024] Step 110, acquiring first power consumption prediction information of instructions of multiple single cores within the prediction window.

[0025] Each single core sequentially reads and executes instructions according to the clock cycle. Instructions within the prediction window are unexecuted instructions on a single core. The length of the prediction window can be multiple clock cycles. Instructions to be executed within the prediction window can be obtained from unexecuted codes according to the av...

Embodiment 2

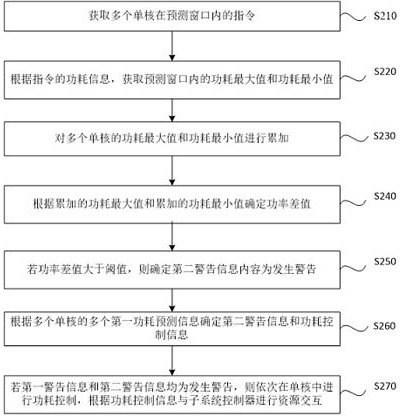

[0067] image 3 The flow chart of the on-chip power consumption management method provided by Embodiment 2 of the present invention serves as a specific description of the foregoing implementation manner. Wherein, step 110, obtaining the first power consumption prediction information of instructions of multiple single cores within the prediction window may be implemented as: obtaining instructions of multiple single cores within the prediction window; obtaining the prediction window according to the power consumption information of the instructions The maximum power consumption and the minimum power consumption within. Step 130, determining the second warning information according to multiple first power consumption prediction information of multiple single cores, may be implemented as: accumulating the maximum power consumption and minimum power consumption of multiple single cores; The maximum value and the accumulated minimum value of power consumption determine the power ...

Embodiment 3

[0082] Figure 4The flow chart of the on-chip power consumption management method provided by Embodiment 3 of the present invention serves as a specific description of the foregoing implementation manner. Wherein, step 110, obtaining the first power consumption prediction information of instructions of multiple single cores within the prediction window may be implemented as: obtaining instructions of multiple single cores within the prediction window; obtaining the prediction window according to the power consumption information of the instructions The average power consumption within. Step 130, determining the second warning information according to multiple first power consumption prediction information of multiple single cores, may be implemented as: accumulating the average power consumption; judging whether the power supply is sufficient according to the accumulated average power consumption; If it is not enough, the content of the second warning message is a warning. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com