High-frequency synchronous power utilization data acquisition device

A technology of power consumption data and acquisition device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

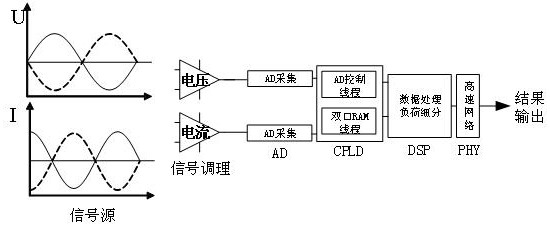

[0039] A high-frequency synchronous power consumption data acquisition device, the first step is to perform analog signal pre-conditioning on the acquisition loop voltage and current signals through a synchronization and filtering signal conditioning circuit;

[0040] The second step is to use the finite state machine method to synchronously control the two highly separated collection AD sampling chips through the programmable logic element CPLD to complete the synchronous 128-point discretization of the voltage and current waveforms;

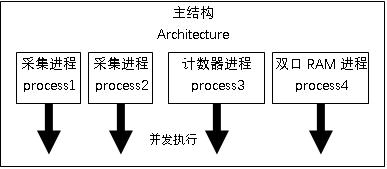

[0041] The third step is to use the programmable logic element CPLD multi-logic element and the ultra-high-speed integrated circuit hardware description language VHDL language multi-threaded module management feature to design a high-speed physical layer protocol PHY chip, so that the signal acquisition data input and signal processing data output are completely synchronized and independent, do not interfere with each other;

[0042] Step 4 is ...

Embodiment 2

[0046] In the high-frequency synchronous electricity data acquisition device described in Embodiment 1, the first step is to first obtain the voltage and current signals of the acquisition loop, and perform phase and amplitude synchronization and summing of the two signals through a typical signal conditioning circuit. Filter, and finally input to the two-way synchronous control two-way highly separated collection AD acquisition chip.

Embodiment 3

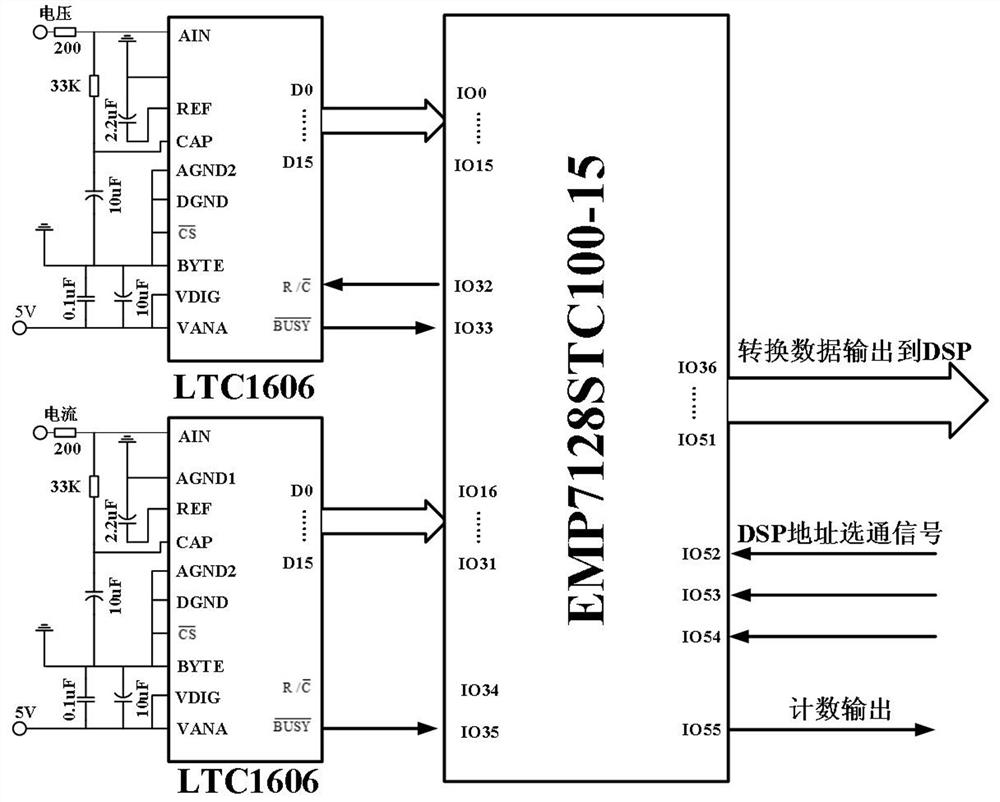

[0048] In the high-frequency synchronous electricity data acquisition device described in Embodiment 1, the second step is to select the high-speed synchronous control two-way highly separated collection AD sampling chip LTC1606 to synchronously acquire the adjusted voltage and current signals, and synchronously control The two-way highly separated collection AD control circuit usually uses a single-chip MCU to synchronously control the control of the two-way highly separated collection AD chip.

[0049]The present invention first considers the synchronization and high-speed acquisition of the two-way signals, and secondly, considers the concurrent management of the subsequent RAM process, so EMP7128STC100-15 is used to control the two-way high-separation high-speed synchronous collection using the programmable logic element CPLD chip. AD performs parallel sampling.

[0050] as attached figure 2 For the sampling control circuit, the programmable logic element CPLD is used to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com