Multi-core starting method based on shared space

A technology of sharing space and space, applied in the field of multi-core startup based on shared space, can solve the problems of not having the conditions for widespread application, high cost, small space occupied by startup programs, etc., saving hardware cost and volume, and low development cost. , the effect of easy transplantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to understand the above-mentioned purpose, features and advantages of the present invention more clearly, the present invention will be further described below in conjunction with the accompanying drawings and embodiments. Many specific details are set forth in the following description to facilitate a full understanding of the present invention. However, the present invention can also be implemented in other ways than those described here. Therefore, the present invention is not limited to the specific embodiments disclosed below.

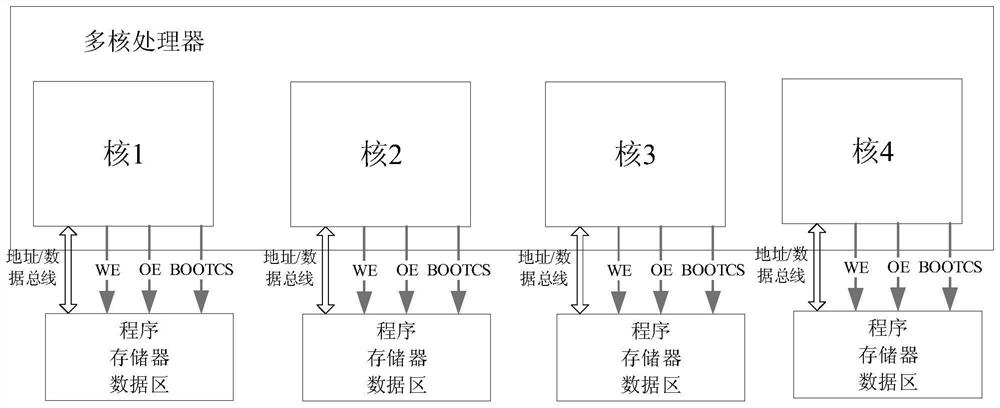

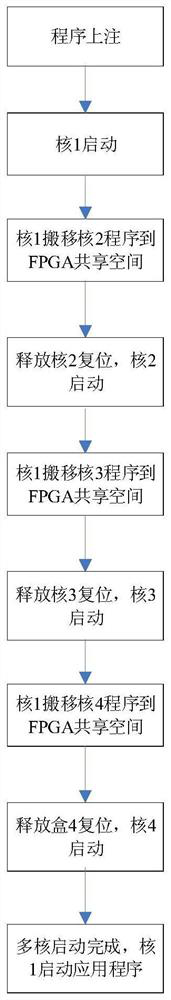

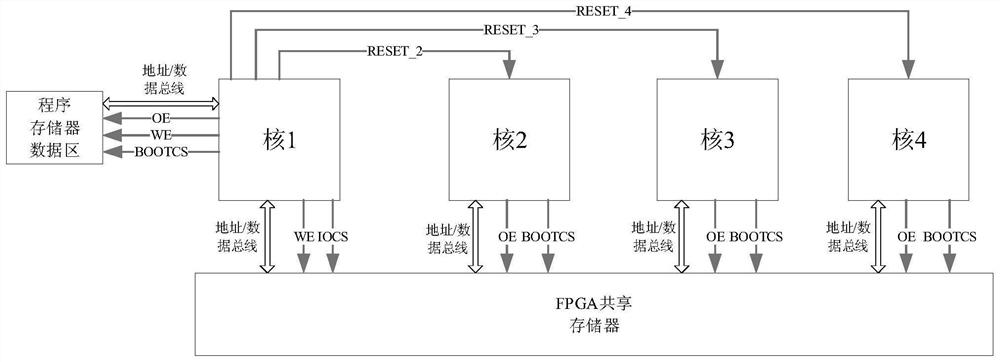

[0022] This program is a more economical and easy-to-implement multi-core software startup technology developed in the use of DSP6713J / 500 multi-core processors. This technology takes the DSP6713J / 500 multi-core processor control computer system as the application object, and supports loading the software of core 2, 3, and 4 through core 1, without configuring a separate FLASH memory for each core. It can save the cost and volume o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com