Global layout method for 2.5D packaged FPGA

A technology of global layout and Poisson equation, used in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as wiring failure and time violation, and achieve the effect of satisfying convergence and speeding up calculation time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

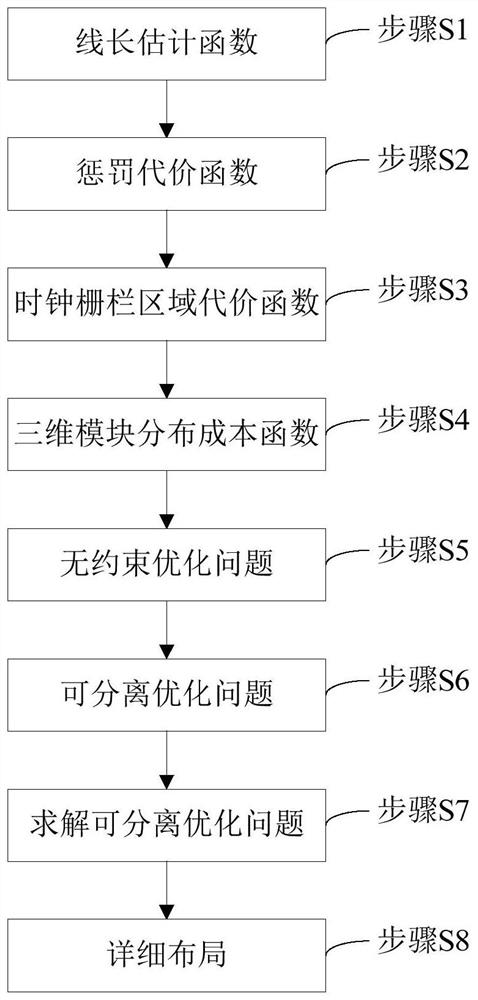

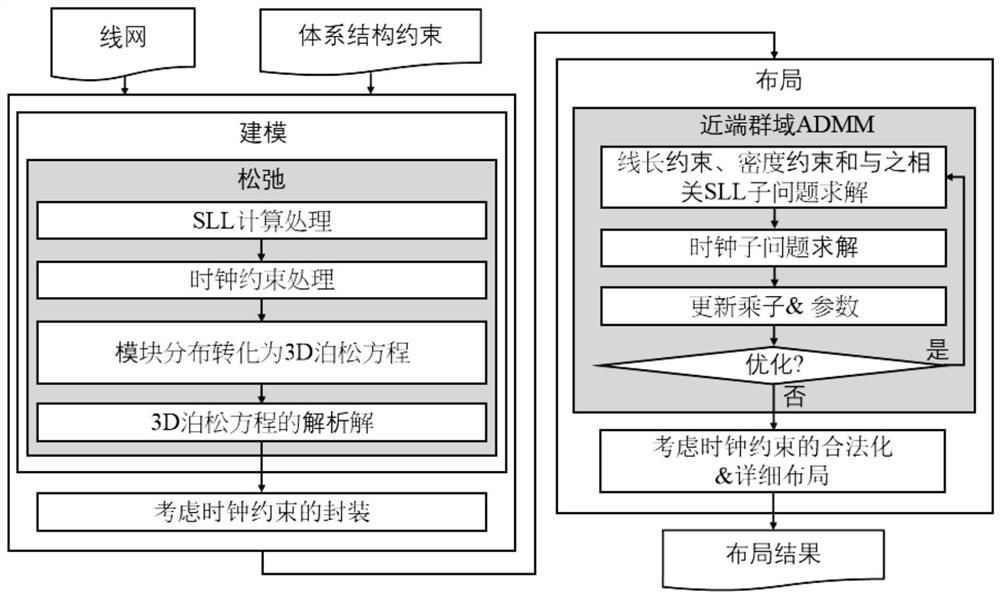

[0085] based on the following figure 1 and figure 2 Preferred embodiments of the present invention will be described in detail.

[0086] The 2.5D package FPGA contains multiple FPGAs, and a single FPGA becomes the super logic area SLR, and the SLR contains multiple logic modules (DSP, CLB, RAM, IO).

[0087] Such as figure 1 As shown, the present invention provides a kind of global layout method for 2.5D packing FPGA, comprises the following steps:

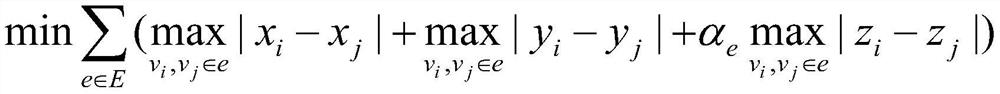

[0088] Step S1, defining a line length constraint condition through a line length estimation function;

[0089] Step S2, constraining the super long line SLL through a continuous penalty cost function;

[0090] Step S3, processing clock constraints through an extended clock fence region cost function;

[0091] Step S4, constraining the module distribution through a three-dimensional module distribution cost function based on the three-dimensional Poisson equation;

[0092] Step S5, expressing the global layout method of 2.5...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com