System and method for establishing simulation model of field effect transistor

A field effect transistor and simulation model technology, applied in special data processing applications, instruments, calculations, etc., can solve problems such as excessive gate current, SPICE simulation convergence problems, affecting the accuracy of JFET models, and ensure accurate simulation. effect of good model properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale. Also, some well-known parts may not be shown.

[0036] In the present application, the term "semiconductor structure" refers to a general designation of the entire semiconductor structure formed in various steps of manufacturing a semiconductor device, including all layers or regions that have been formed.

[0037] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

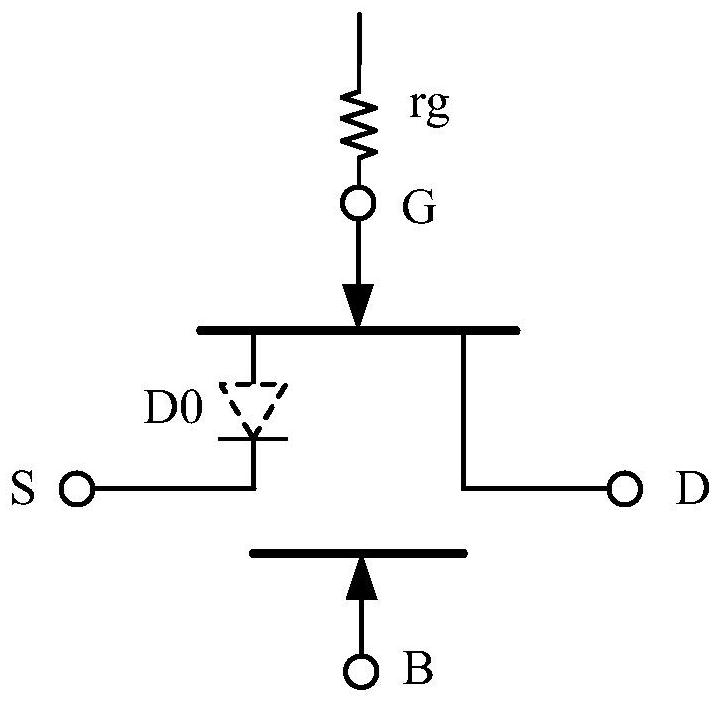

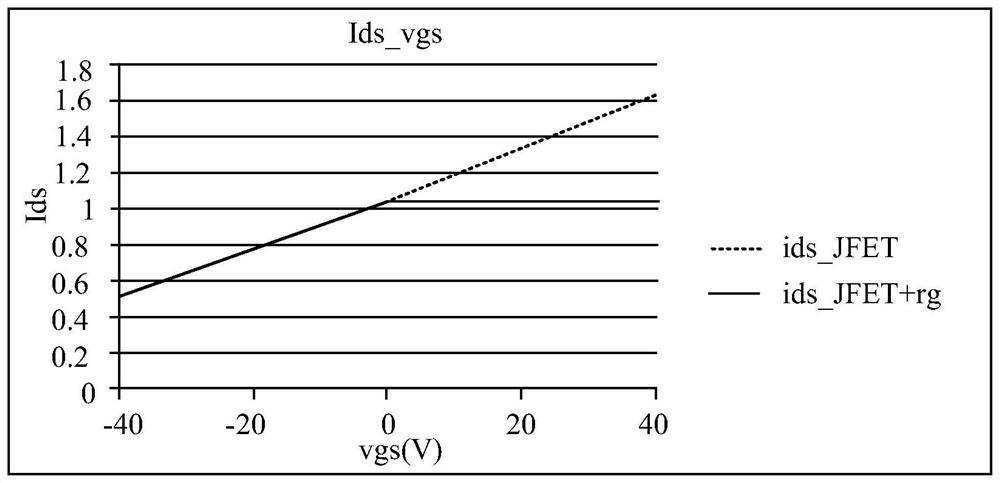

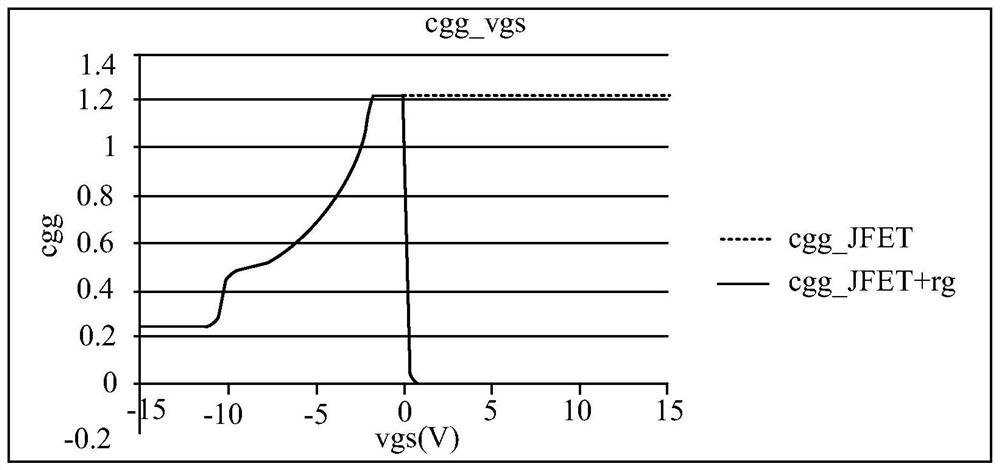

[0038] figure 1 Schematic diagram of the simplified structure of the JFET model showing the gate series resistance; Figure 2a and Figure 2b respectively show the basis of figure 1 The cur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com