Clock crossing FIFO status converged synchornizer

A clock, state technology, used in instruments, pulse counters, counting chain pulse counters, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

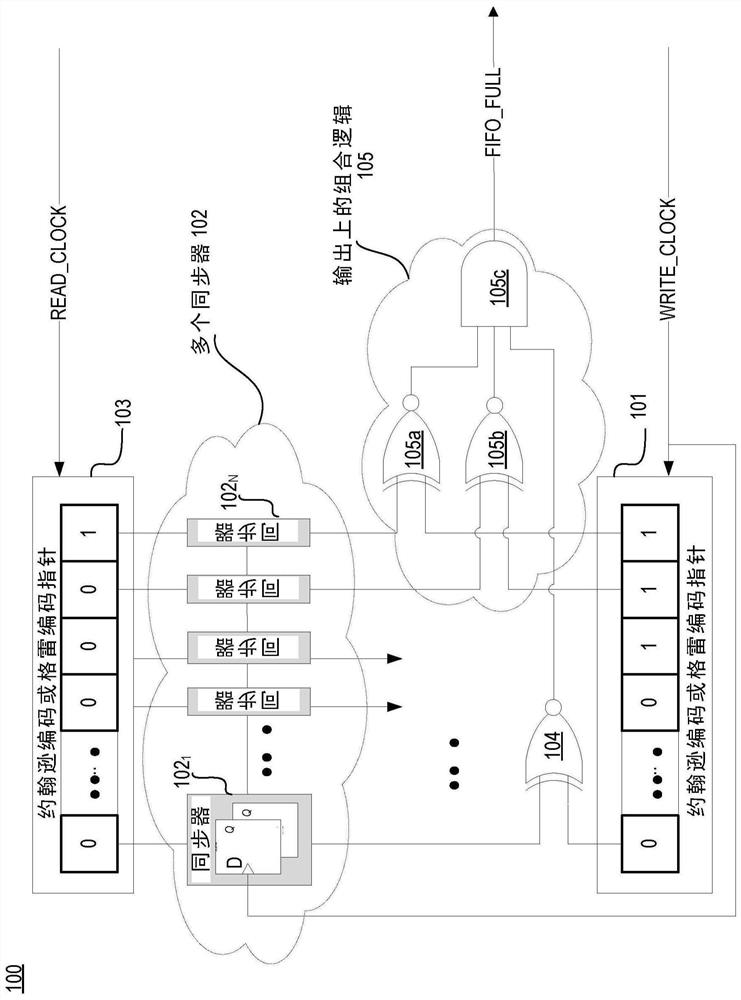

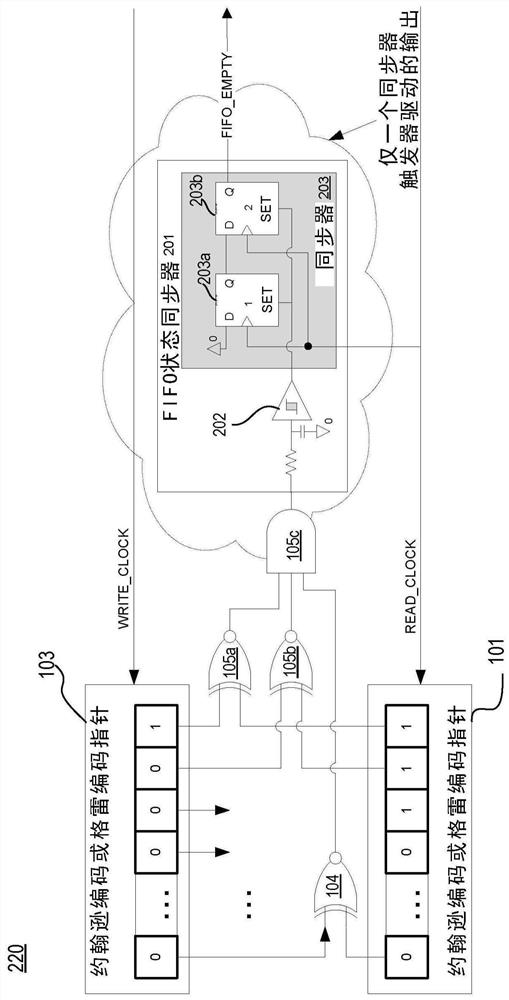

[0121] Example 1: An apparatus comprising: a pipeline; a first set of pointers associated with the pipeline, wherein the first set of pointers is associated with a read clock for reading from the pipeline; a second set of pointers associated with the pipeline, wherein , the second set of pointers is associated with the write clock for the write pipeline; a comparator for comparing the first set of pointers with the second set of pointers; logic coupled to the output of the comparator, where the logic performs an AND operation a filter coupled to the output of the logic; a Schmitt trigger coupled to the filter; at least two flip-flops coupled to the Schmitt trigger, wherein the output of at least one of the two flip-flops is indicative of a pipeline status.

example 2

[0122] Example 2: The apparatus of example 1, wherein the comparator comprises logic gates to perform an exclusive-or operation or an exclusive-or-not operation.

example 3

[0123] Example 3: The apparatus of example 1, wherein the output of the Schmitt trigger is used to set or reset the output of at least two flip-flops.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com