Low-power-consumption FPGA (Field Programmable Gate Array) partially reconfigurable method and low-power-consumption FPGA partially reconfigurable device

A low-power, reconfigurable system technology, applied in the architecture with a single central processing unit, digital computer components, digital data processing components, etc., can solve the problem of reconfigurable and ineffective power consumption, and avoid heat dissipation and stability issues, the effect of reducing ineffective power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

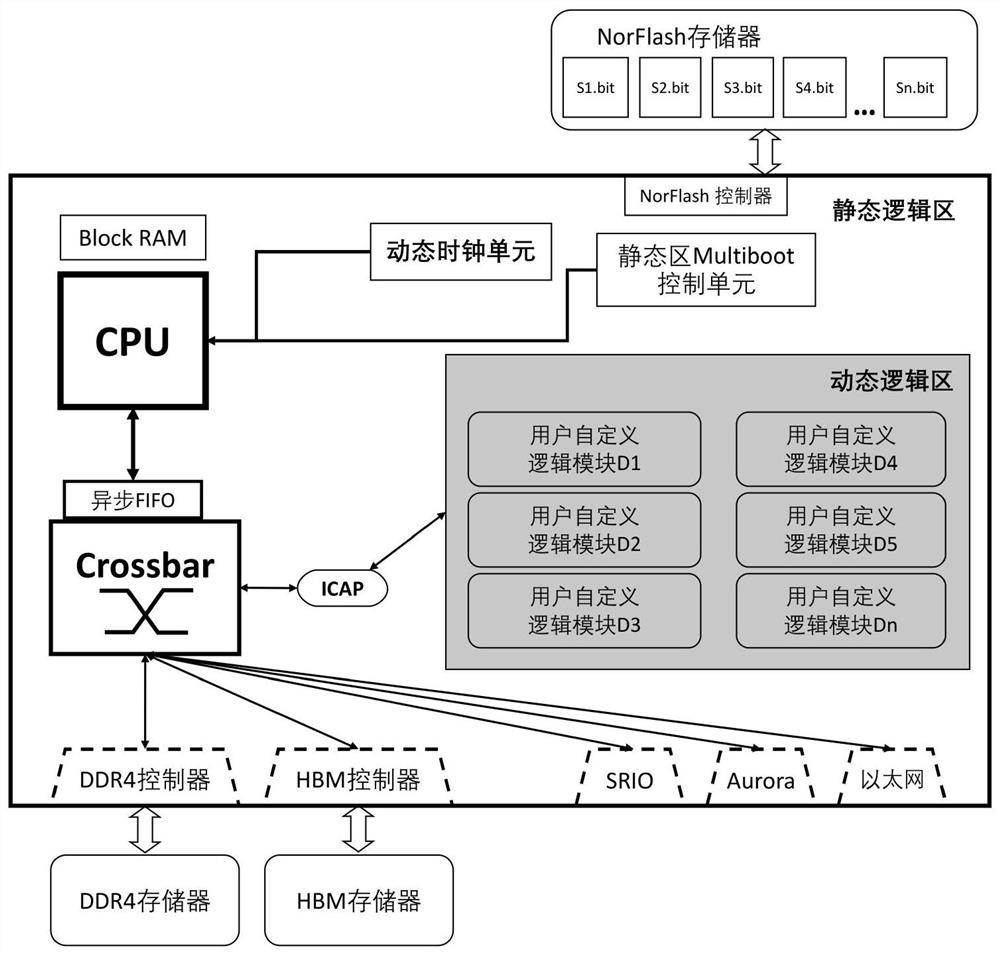

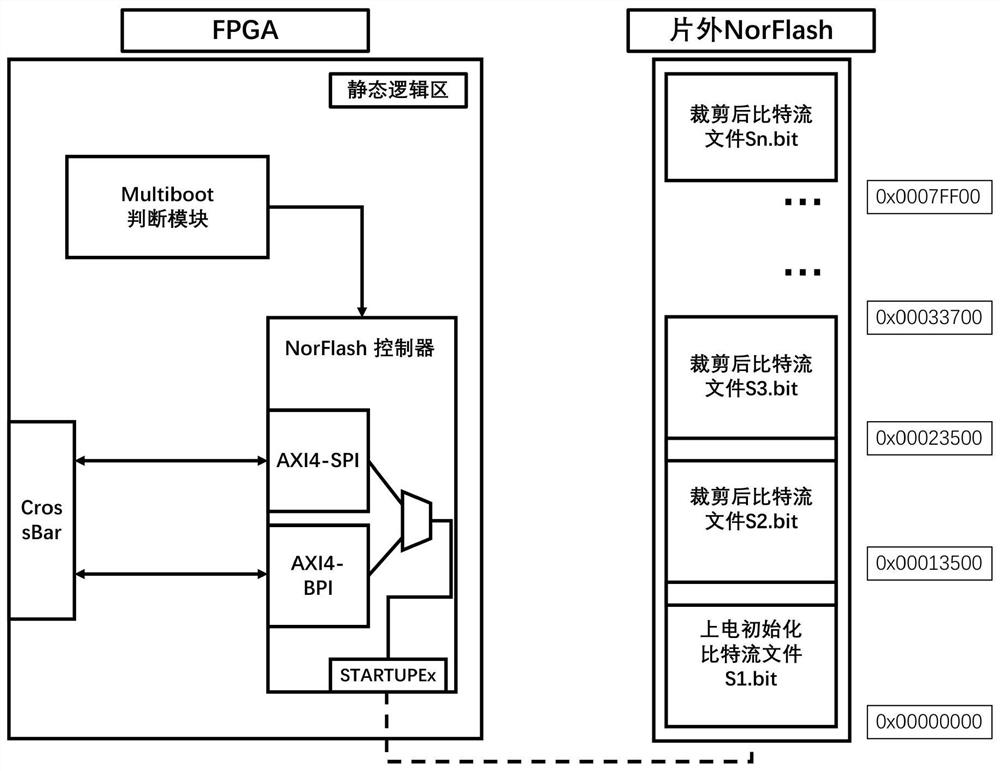

[0033]The inventor analyzed the configuration scheme of the static logic area and the dynamic logic area, and the composition of the power consumption of the static area, and proposed that the reduction of ineffective power consumption can be solved from two aspects:

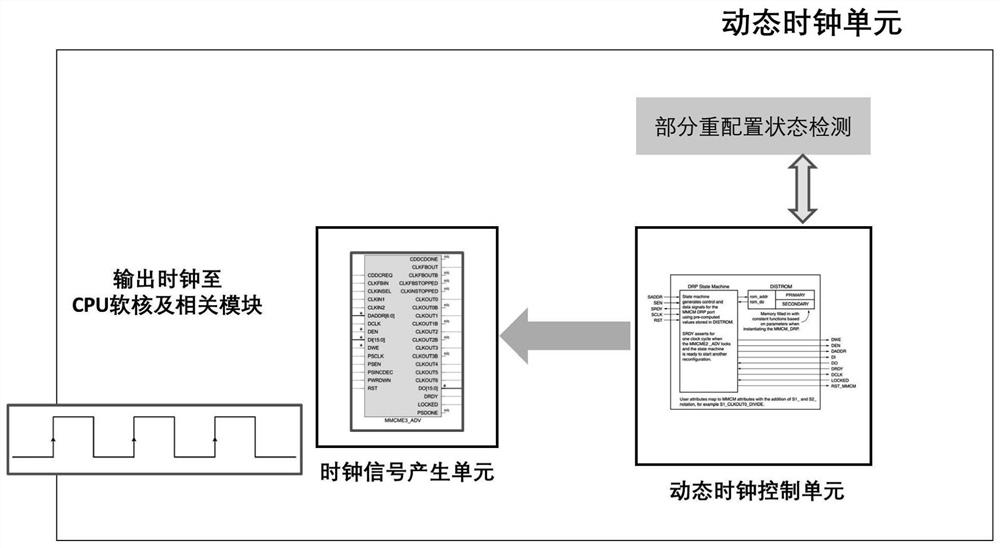

[0034] The first aspect is to dynamically reduce the clock frequency of the logic in the static area to reduce the dynamic power consumption of the circuit caused by unnecessary high operating frequency, that is, to replace the static clock in the current industry solution by setting a dynamically reconfigurable clock unit Unit, which dynamically adjusts the clock of the CPU in the static logic area to reduce its power consumption in the idle state;

[0035] The second aspect is to flexibly reduce the idle power consumption of the external controller interface in the logic of the static area. According to the way the cloud service is provided, it is divided into two types of sub-scenarios:

[0036] In the scena...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com