Multi-path transmission data bus redundancy synchronous communication method

A data bus and synchronous communication technology, applied in the direction of electrical digital data processing, inter-program communication, multi-program device, etc., can solve the problems of long recovery time of working status, single point of bus controller interface, etc., and improve reliability and safety effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

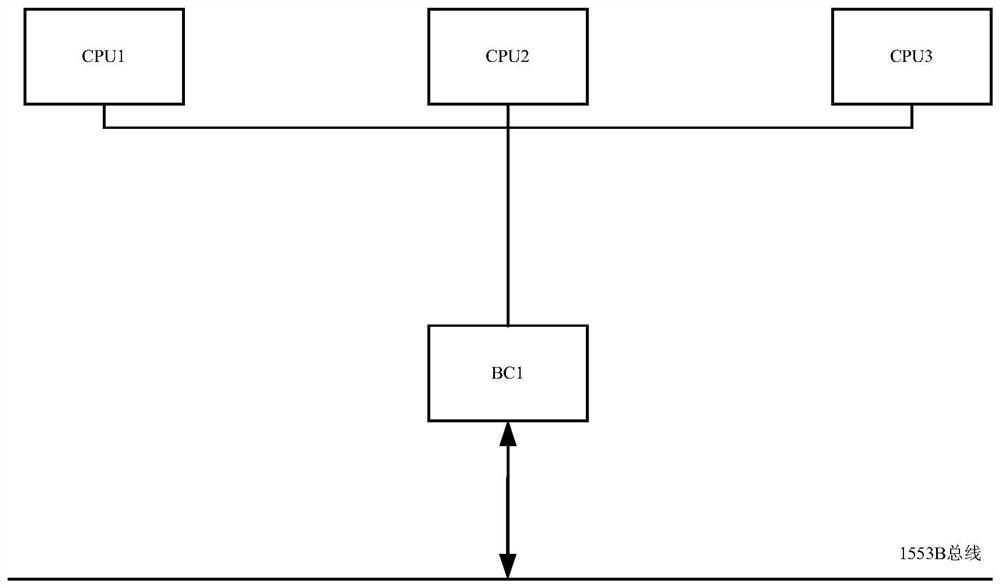

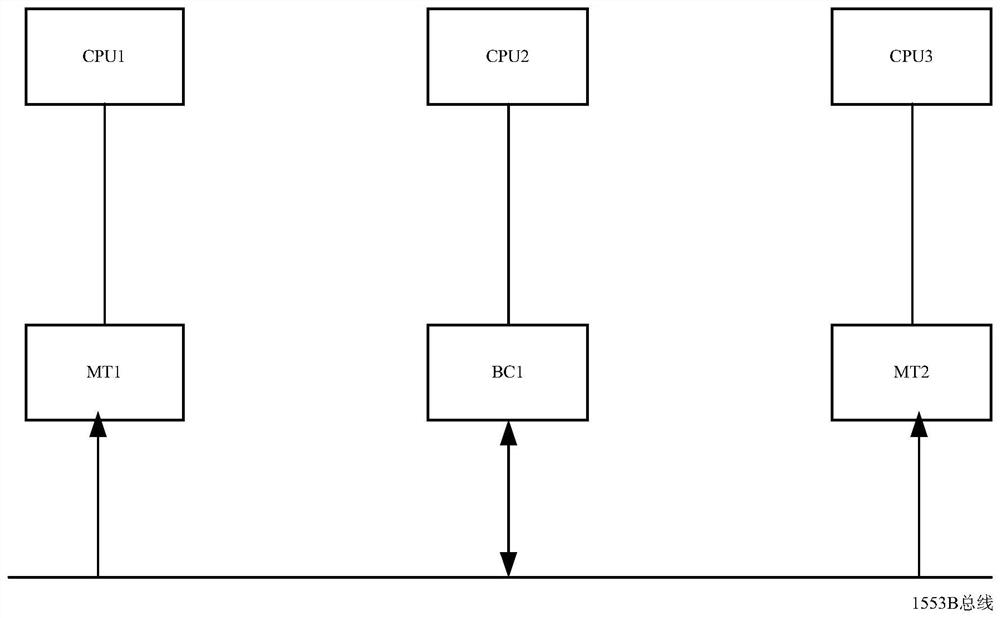

[0038] Embodiment 1, the multiplex data bus redundant synchronous communication method described in the present application, adopts such as Figure 4 In the bus interface mode shown, the three-mode redundant computer has three CPUs (that is, three mutually redundant computer modules), of which there is only one master, and the rest are slaves by default when powered on. When it is detected that the current chip fails, the host can choose any of the 3 computer modules at any time.

[0039] Specifically, host switching is realized by rewriting the program instructions of the FPGA.

[0040] The single machine where each CPU is located has an independent bus communication chip, and the working mode of the 1553B bus is configured as BC mode, and all of them are connected to the bus communication network.

[0041] Using the above-mentioned bus interface mode, this application mainly adopts the following three solutions: 1. Only one terminal should control the bus system at any time...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com