True random number generator and electronic equipment

A true random number and generator technology, applied in the field of information security, which can solve the problems of metastable generation and difficulty in use.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0034] In order to realize the generation of random numbers based on metastable states, an embodiment of the present application provides a true random number generator.

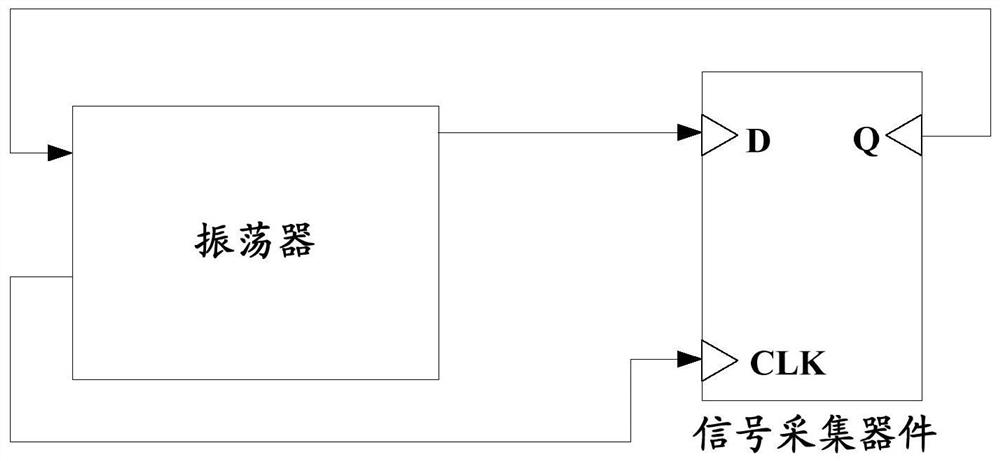

[0035] see figure 1 As shown, the true random number generator provided by the embodiment of the present application includes two parts: a signal acquisition device and an oscillator.

[0036] It should be noted that the signal acquisition device used in the embodiment of the present application includes a data acquisition port (D port), a clock port (CLK port) and an output port (Q port). Among them, when the signal acquisition device is in the normal working state (that is, in the non-metastable state), the output port will output the corresponding output value according to the input level value of the input port, and the clock port is used to trigger the "output port According to the input level value of the input port, output the corresponding output value". That is, when a valid signal is input to the...

Embodiment 2

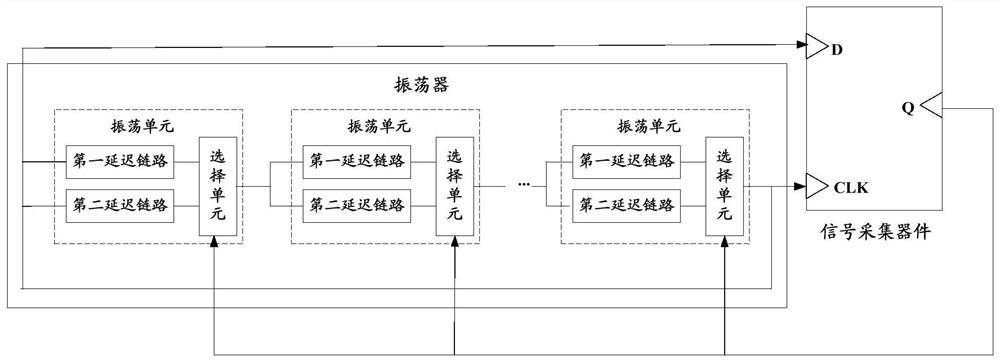

[0079] In this embodiment, on the basis of the first embodiment, a specific true random number generator structure is used to further illustrate the solution of the present application.

[0080] see Figure 8 The true random number generator shown,

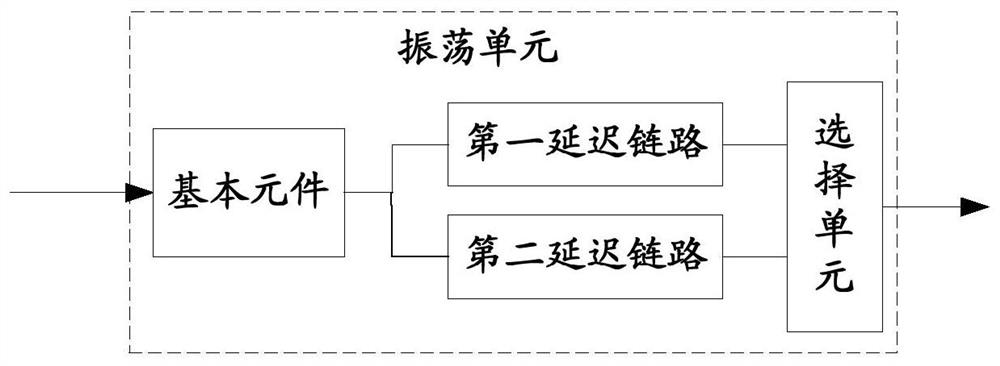

[0081] 101 and 102 are delay links.

[0082] 103 is a delay link (fast dly) with a higher frequency (smaller delay period) than 104 .

[0083] 104 is a delay link (slow dly) with a slower frequency (larger delay period) than 103 .

[0084] 105 is two-way selector (MUX2), when the S=1 that D flip-flop 109 outputs, MUX2 sends the data of 1 port to output, when the S=0 that D flip-flop 109 outputs, MUX2 sends the data of 0 port sent to the output.

[0085] 106 is a D flip-flop (DFF). Its CLK port (clock port) and D port (data acquisition port) will receive a rising edge signal at the same time.

[0086] 107 is an output port of DFF106, which is a port for generating random numbers when DFF106 is in a metastable state.

[0087]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com