Manufacturing method of low-voltage high-density trench DMOS device

A device manufacturing method and high-density technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of being easily pierced by holes and low product yield, and reduce the short circuit problem of polysilicon through the gate , Improve product yield and reliability, optimize process effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0031] The invention provides a method for manufacturing a low-voltage high-density trench DMOS device, comprising the steps of:

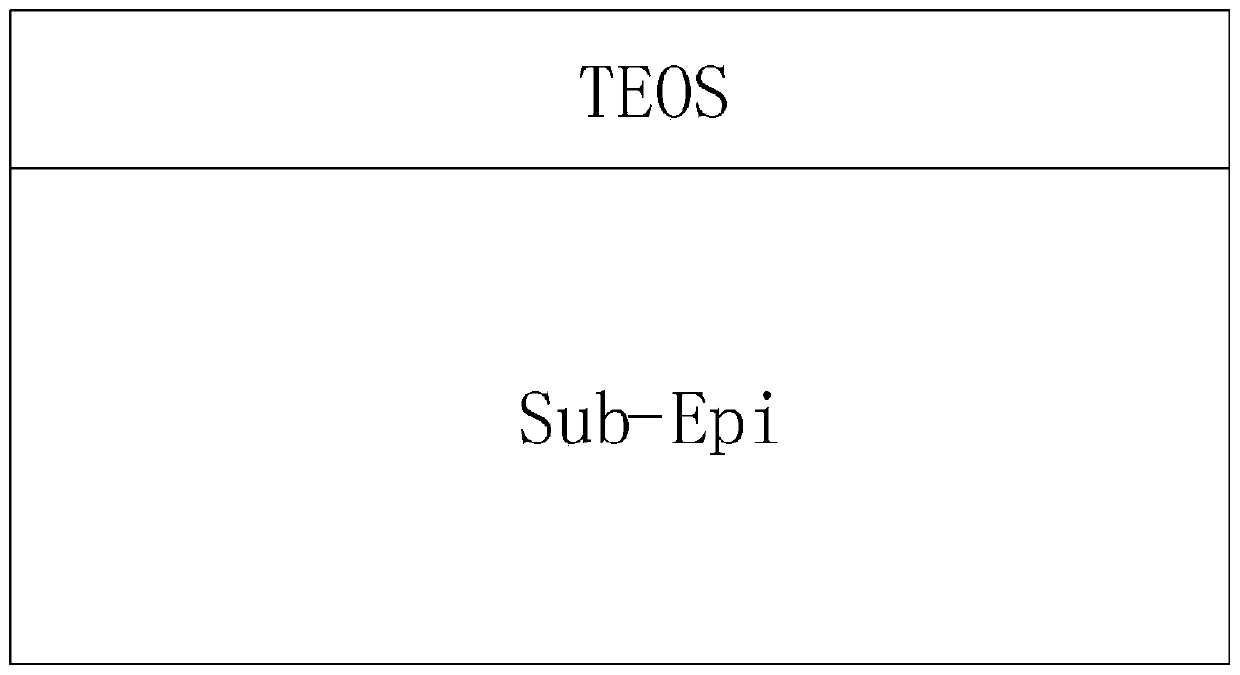

[0032] Deposit a layer of oxide layer on a suitable epitaxial material. In the first embodiment, silicon is selected as the epitaxial material, and the deposited oxide layer is TEOS material. The height of the TEOS material is 4000~8000Å, such as figure 1 shown;

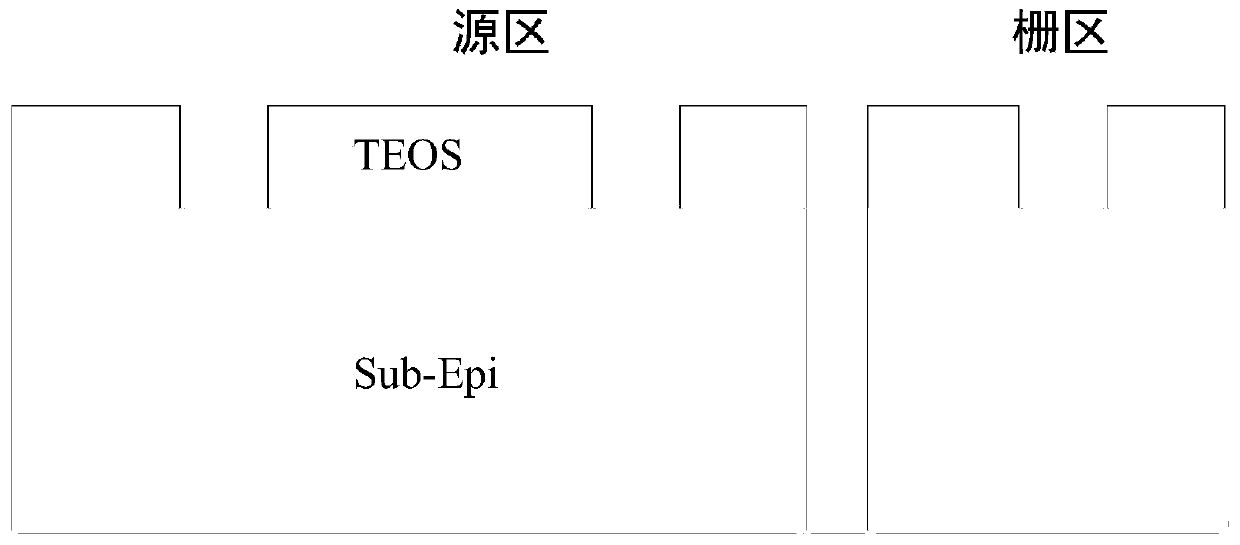

[0033] Using photolithography and dry etching process on the silicon material, first etch the oxide layer, such as figure 2 shown;

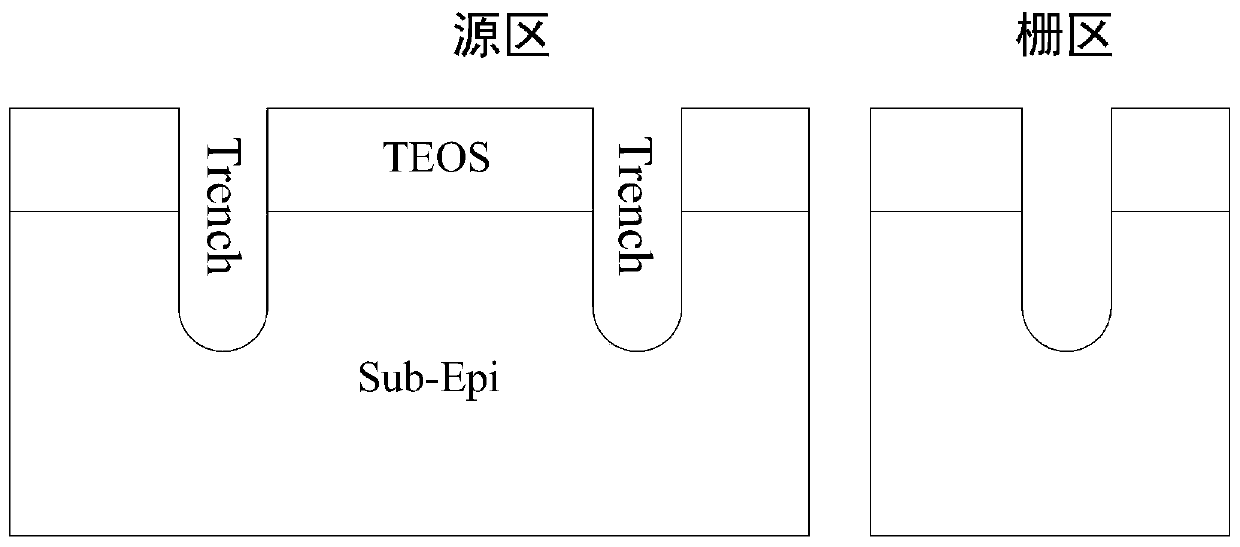

[0034] Use the remaining oxide layer as a mask layer to etch the trench array, such as image 3 ;

[0035] Retain the oxide layer as a masking layer, remove the surface silicon damage in the trench array through a sacrificial oxidation process, use thermal oxidation to grow a gate oxide layer with a certain thickness, and deposit polysilicon gate Poly in the trench array, such as Figure 4 shown;

[0036] Use the dry etching back process to etch away t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap