A kind of 3D NAND memory structure and preparation method thereof

A 3DNAND, storage structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as storage area loss, and achieve the effects of increasing storage area, improving stress resistance, and reducing parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

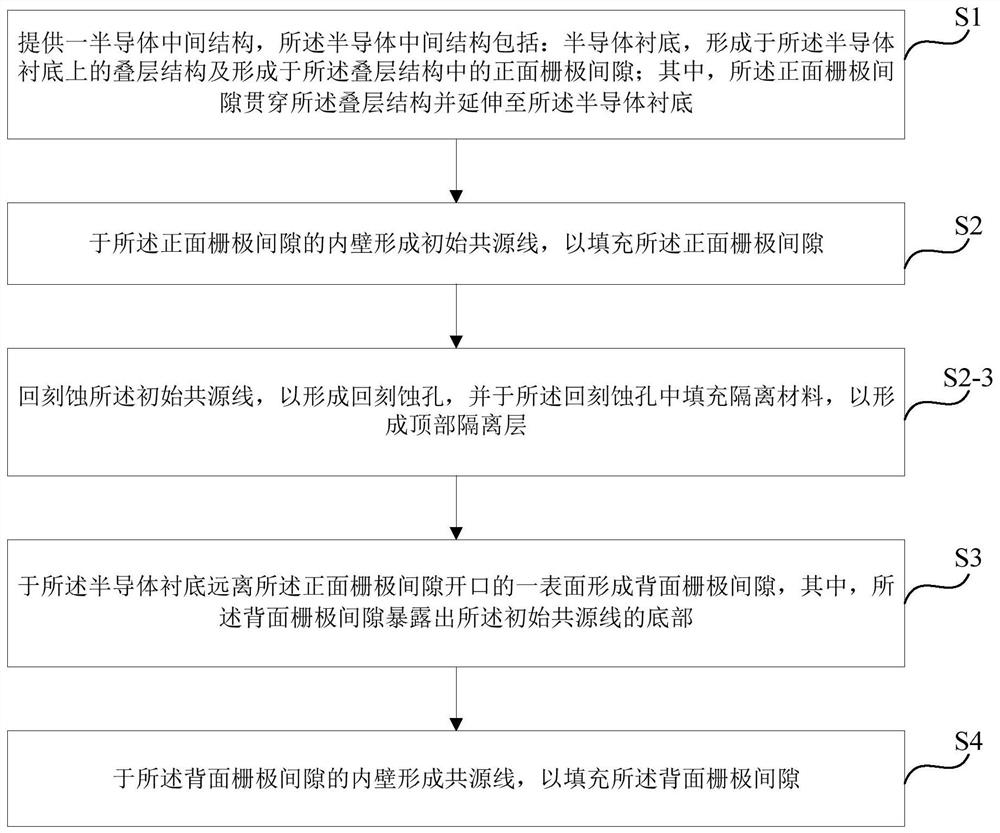

[0124] Such as figure 1 As shown, the present embodiment provides a method for preparing a 3D NAND storage structure, the preparation method comprising:

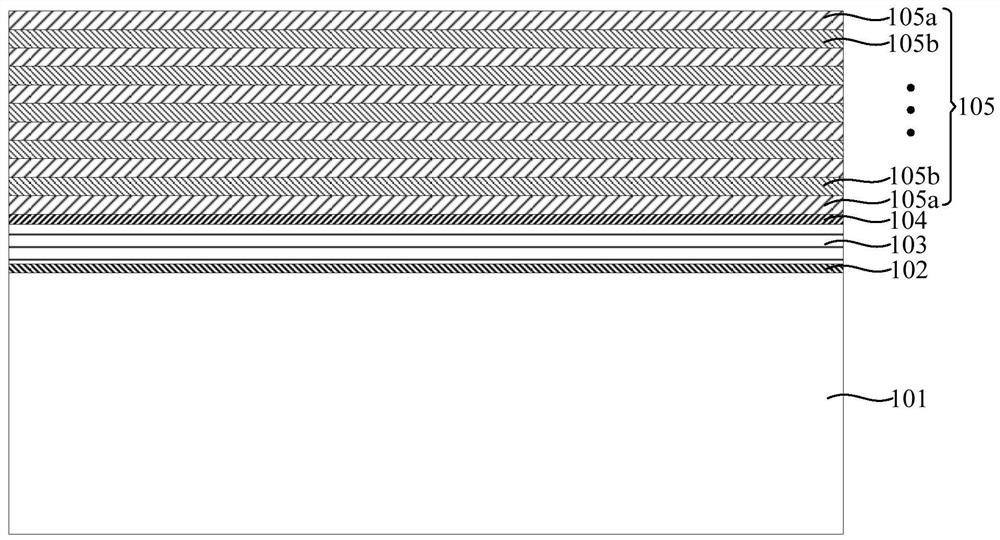

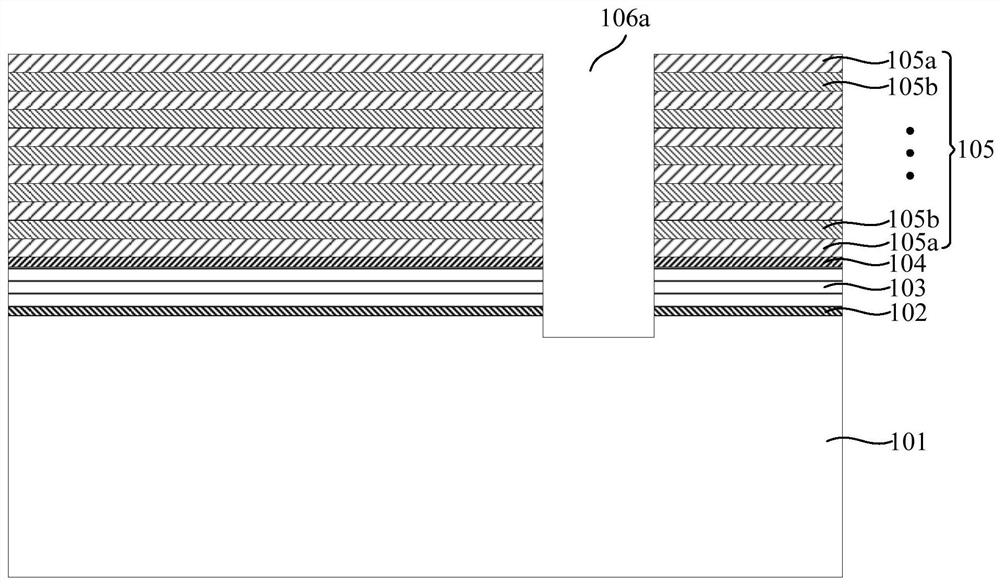

[0125]S1: Provide a semiconductor intermediate structure 10, the semiconductor intermediate structure 10 includes: a semiconductor substrate 101, a stacked structure 116 formed on the semiconductor substrate 101 and a front gate formed in the stacked structure 116 A gap 112; wherein, the front gate gap 112 runs through the stacked structure 116 and extends to the semiconductor substrate 101;

[0126] S2: forming an initial common source line 13 on the inner wall of the front gate gap 112 to fill the front gate gap 112;

[0127] S3: forming a back gate gap 16 on a surface of the semiconductor substrate 101 away from the opening of the front gate gap 112, wherein the back gate gap 16 exposes the bottom of the initial common source line 13;

[0128] S4: forming a common source line 19 on the inner wall of the back gate gap 16...

Embodiment 2

[0194] Such as Figure 23 As shown, the present embodiment provides a 3D NAND storage structure, and the storage structure includes:

[0195] The semiconductor intermediate structure 10, the semiconductor intermediate structure 10 includes: a semiconductor substrate 101, a stacked structure 116 formed on the semiconductor substrate 101, and a front gate gap 112 formed in the stacked structure 116, wherein , the front gate gap 112 runs through the stacked structure 116 and extends to the semiconductor substrate 101;

[0196] an initial common source line 13 formed in the front gate gap 112;

[0197] a back gate gap 16 formed in the semiconductor substrate 101, wherein the back gate gap 16 exposes the bottom of the initial common source line 13;

[0198] The common source line 19 is formed in the back gate gap 16 .

[0199] Since the 3D NAND storage structure described in this example forms a back gate gap 16 on the back side of the semiconductor substrate 101 and leads a com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com