3D NAND memory and manufacturing method thereof

A 3D NAND and manufacturing method technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of limited grid line gap size, affecting the use of devices, leakage, etc., to facilitate formation, reduce time, and reduce production costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0095] This embodiment provides a method for manufacturing a 3D NAND memory, such as image 3 As shown, the method includes the following steps:

[0096] Step S101: Provide a substrate, on which a stack structure of alternately stacked sacrificial layers and isolation layers is formed, wherein the first sacrificial layer close to the substrate is a common-source sacrificial layer, and the stack structure includes several storage Block areas, each memory block area includes a through hole area, the through hole area includes a first gate line gap area, and several memory block areas are divided by the second gate line gap area;

[0097] Provide a substrate 100, the material of the substrate 100 can be single crystal silicon (Si), single crystal germanium (Ge), or silicon germanium (GeSi), silicon carbide (SiC); it can also be silicon on insulator (SOI) , germanium on insulator (GOI); or other materials, such as III-V group compounds such as gallium arsenide. In this embodimen...

Embodiment 2

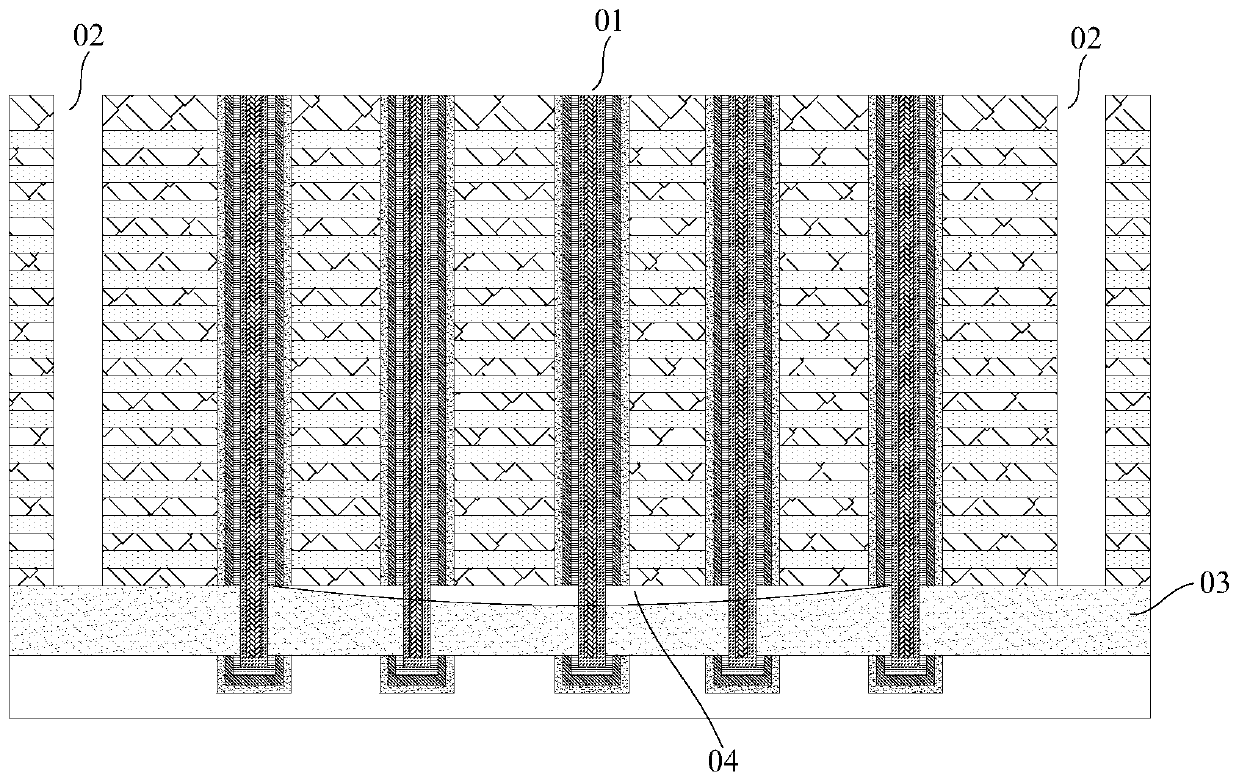

[0110] This embodiment provides a kind of 3D NAND memory, refer to the attached Figure 4 ~ attached Figure 17 , the 3D NAND memory includes:

[0111] A substrate 100, on which a stacked structure 101 is formed, the stacked structure is formed by alternating arrangement of gate layers 110 and isolation layers, and the stacked structure includes several memory blocks; in this embodiment, the gate conductive material can be It is a metal material, such as tungsten, etc.

[0112] A selective epitaxial structure 108 is formed between the substrate and the stack structure. The epitaxial structure 108 in this embodiment has a uniform structure without defects such as gaps, thereby avoiding risks such as electric leakage in the later stage of the device. as well as

[0113] A plurality of first array common sources formed in the storage block are distributed at intervals in the first direction.

[0114] In this embodiment, the material of the substrate 100 can be single crystal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com