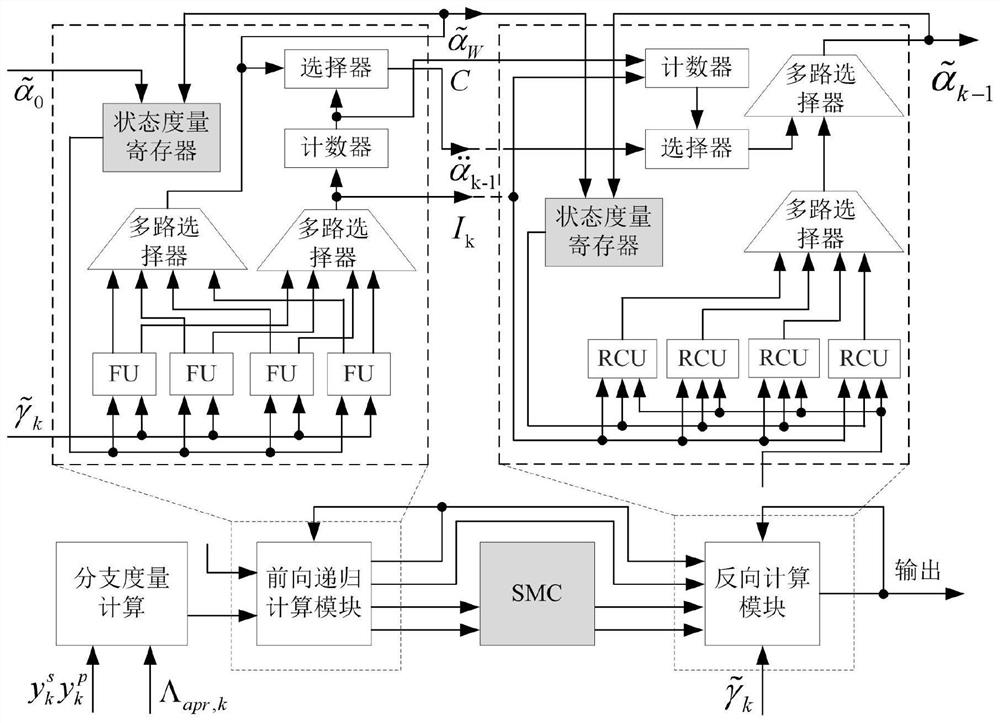

A turbo code decoder and processing method based on reverse butterfly calculation

A butterfly computing and decoder technology, applied in the Turbo code decoding structure and processing field based on reverse butterfly computing, can solve the problems of turbo code decoder power consumption, low storage capacity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

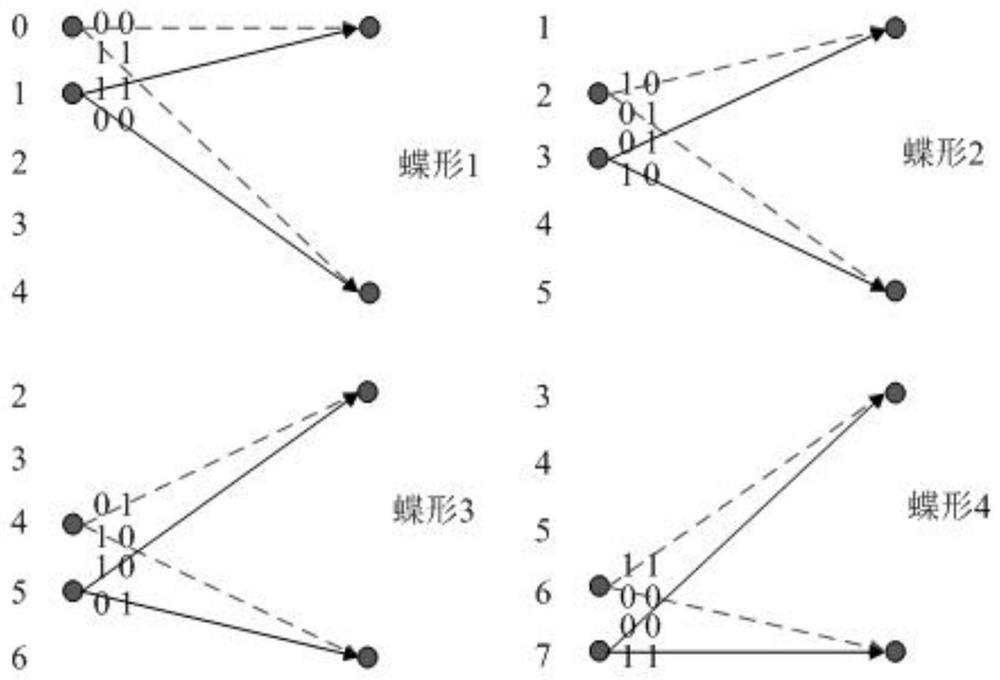

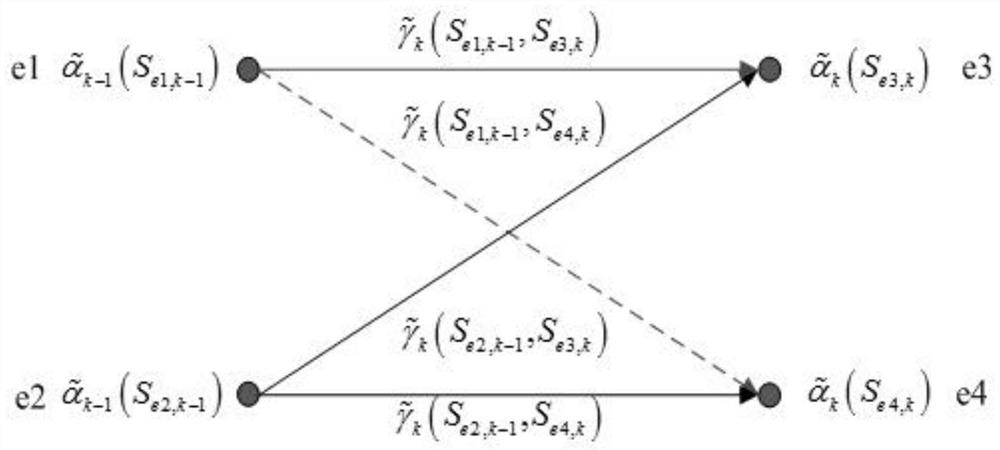

Method used

Image

Examples

Embodiment 1

[0077] Take the FPGA implementation of the Turbo code decoder under the LTE-Advanced standard as an example; the selected code length is 1024, the code rate is 1 / 3, the FPGA chip uses the EP4CE75F23C8 target device, the programming language is Verilog HDL, and the QuartusⅡ13.1 platform is used Carry out Turbo code decoder implementation. The use of the total storage capacity obtained by simulating the full compilation of the forward state metric calculation part shows that the total storage capacity consumed by the traditional direct storage of 8 state metrics is 2560 bits, while the total storage capacity consumed by our proposed method is The storage capacity is 896bits, so the SMC is effectively reduced by 65%.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com