A kind of multi-line scan line feed display method and chip

A line display and chip technology, applied in the field of multi-line scan and line feed display methods and chips, can solve the problems of low grayscale clock GCLK frequency, poor display picture quality, inability to display high grayscale levels, etc., so as to improve the display grayscale. Level, Dependency Reduction, Enhanced Display Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

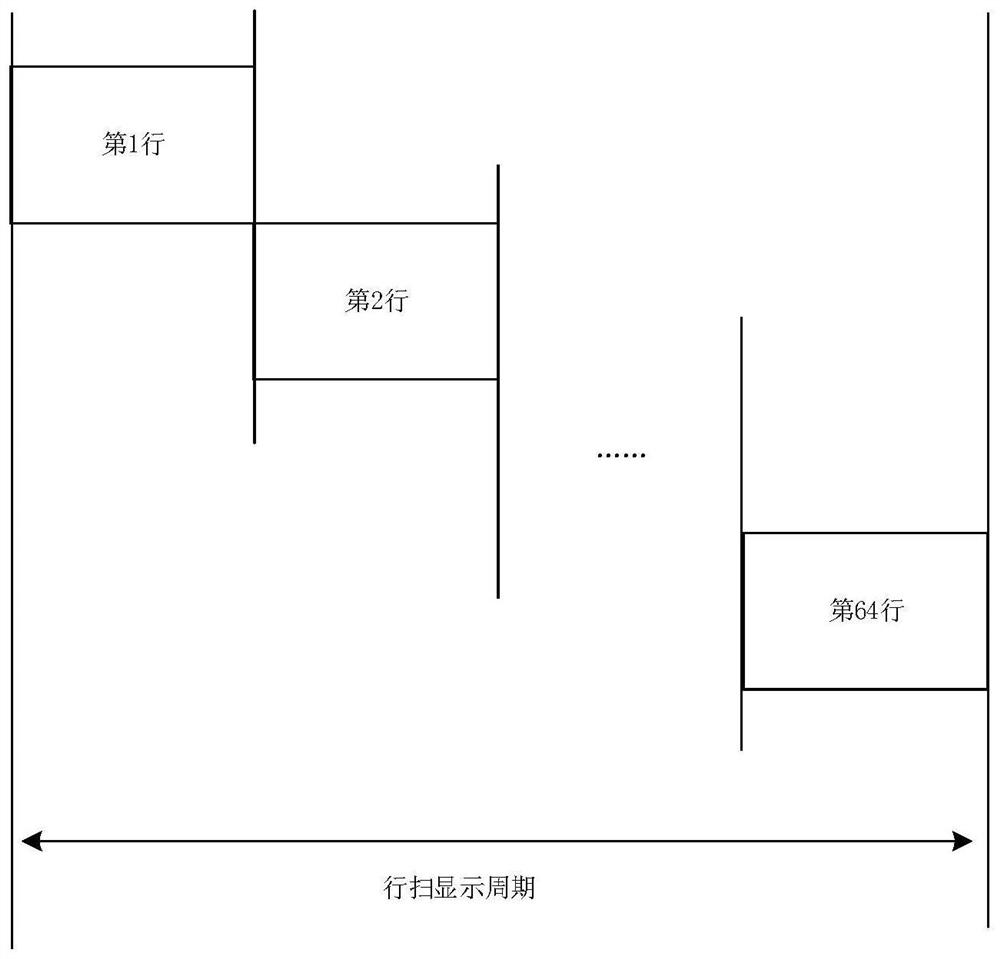

[0040] Figure 4 Shown is a schematic diagram of line feed timing in the prior art, where the grayscale clock GCLK is sent to the chip by an external control card. The principle of line-wrapping display in the prior art is not to display data when the grayscale clock GCLK is not received, and to display the data of this line when the grayscale clock GCLK is received, so as to realize the display of multiple lines of data. This method is limited by external hardware factors such as the layout and wiring of the PCB board, and the frequency of the grayscale clock GCLK cannot be made very high. According to the formula: grayscale = grayscale clock GCLK frequency / (frame frequency * line scan number ), the gray-scale clock GCLK remains unchanged, and when the line scan number increases, the gray-scale level decreases. And the existing technology is equivalent to relying on the external grayscale clock GCLK for line feed and display, which requires high PCB board manufacturing. Fo...

Embodiment 2

[0052] This embodiment introduces its gray scale data display method in detail based on the constant current chip described in Embodiment 1.

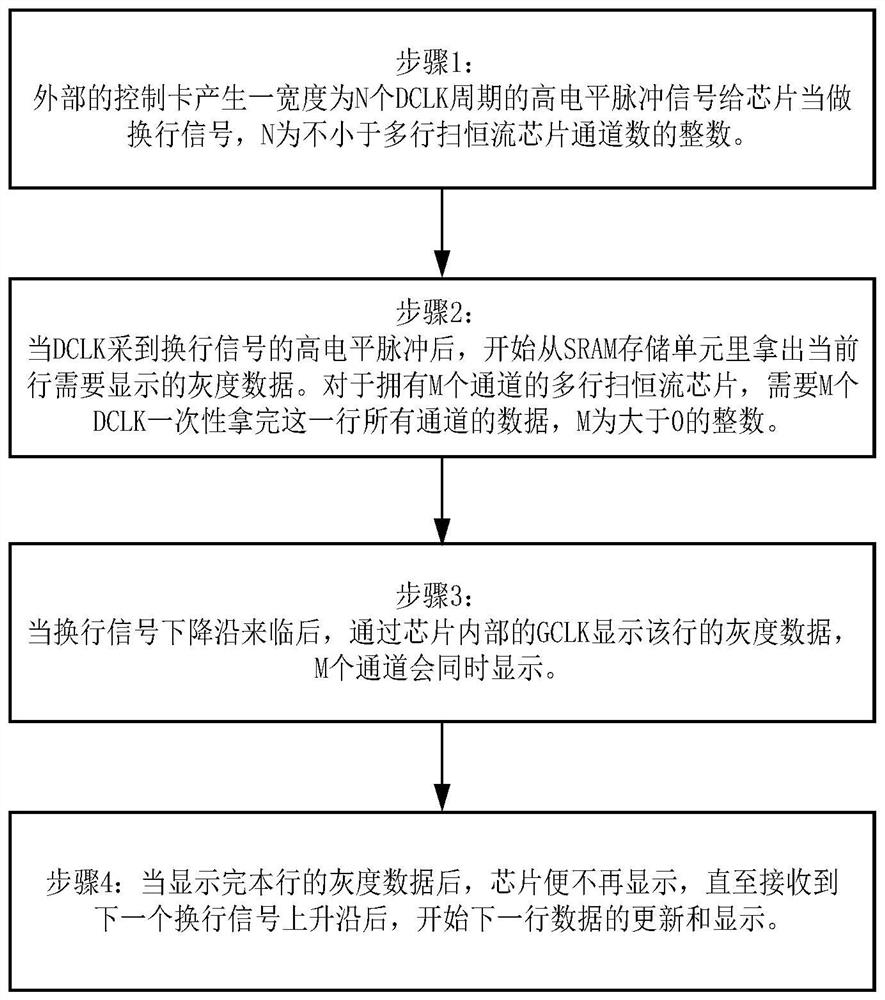

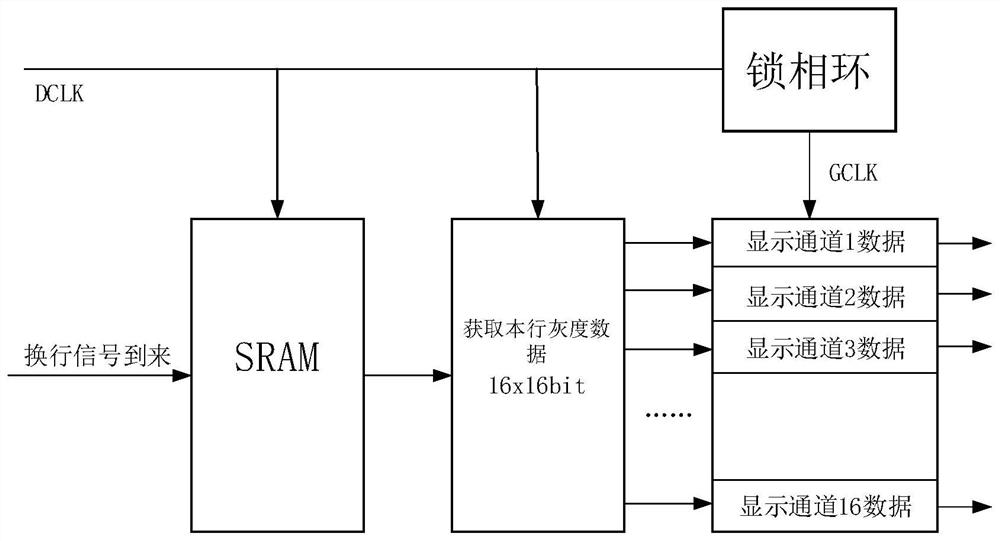

[0053] figure 1 A schematic flow chart of the display method for the constant current chip, including the following steps:

[0054] Step 1: The external control card generates a high-level pulse signal to the chip as a line feed signal. The width of the high-level pulse signal is N data clock DCLK cycles, and N is an integer not less than the number of channels of the multi-line sweep constant current chip. . Figure 5 For the timing diagram of line feed display in the present invention, taking a 16-channel constant current chip as an example, the number of channels is 16, so the minimum high pulse width of the line feed signal is 16 data clock DCLK clock cycles.

[0055] The pulse width of the line feed signal is set according to the number of channels of the multi-line scanning constant current chip. When displaying, the data of eac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com