Debugging verification platform and test method for RISC-V processor system

A RISC-V, processor system technology, applied in fault hardware testing methods, electrical digital data processing, instruments, etc., can solve the problems of cumbersome SoC verification platform construction and high requirements for boards and cards, so as to improve project parallelism and flexible debugging High performance and low hardware resource requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

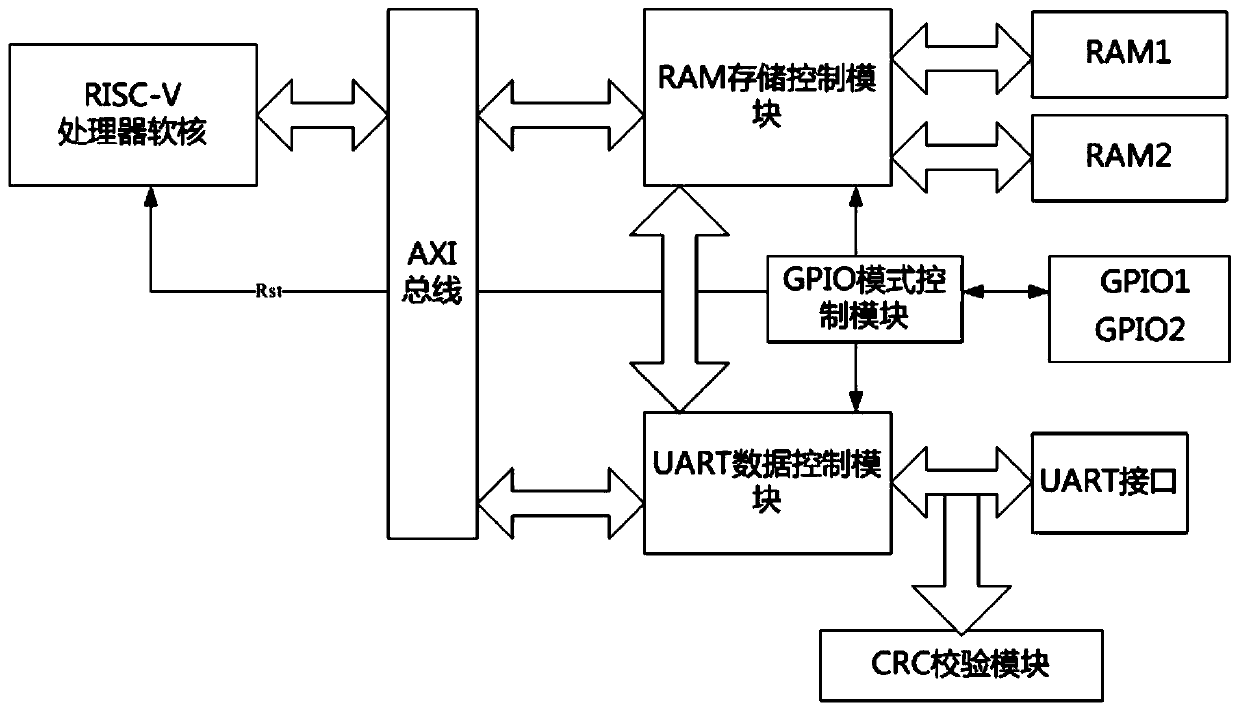

[0045] like figure 1 As shown, the technical solution of the present invention provides a debugging verification platform of a RISC-V processor system, and the FPGA-based RISC-V processor system starts the SoC verification platform, including a processor soft core, and the processor soft core passes through the bus The module communicates with the RAM storage control module and the UART data control module respectively;

[0046] The platform also includes a mode control module, and the mode control module is connected with the RAM storage control module and the UART data control module respectively;

[0047] The RAM storage control module is connected with a RAM memory; it is used for code instruction storage and program operation;

[0048] The mode control module is connected with a GPIO interface, which is used to generate a control signal to the processor soft core for system mode conversion according to the input signal of the GPIO interface;

[0049]The UART data contro...

Embodiment 2

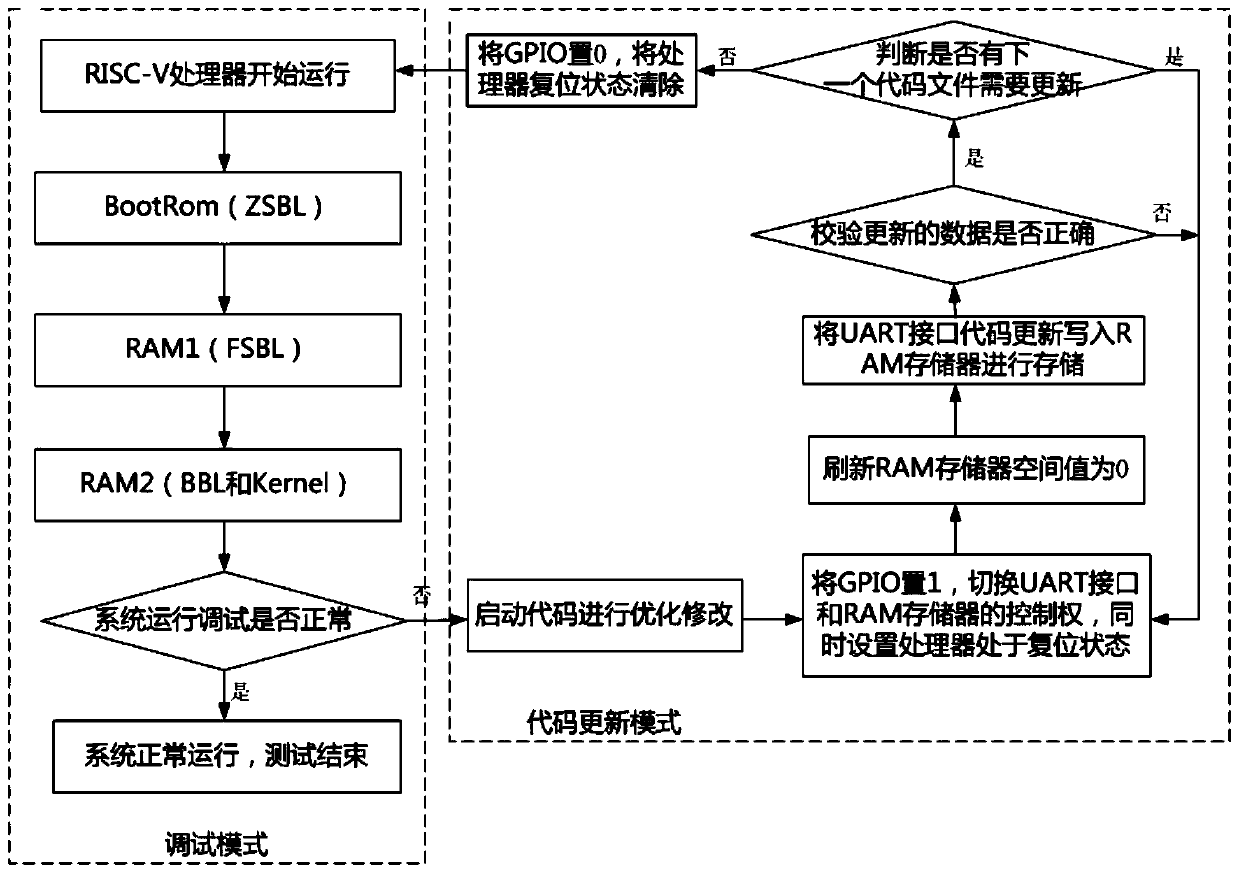

[0062] like figure 2 As shown, the technical solution of the present invention provides a testing method for a debugging system of a RISC-V processor system. For the debugging platform of Embodiment 1, the RISC-V system startup testing method according to the present invention can be divided into debugging according to GPIO control and update two modes, including the following steps:

[0063] S1: The RISC-V processor starts running;

[0064] S2: The startup code starts to run;

[0065] For the RISC-V processor soft core, it is necessary to correctly configure its operating frequency, BootRom address and RAM bus address. The system startup code includes ZSBL, FSBL, BBL and Kernel. In order to save storage resources, optimize the invalid code as much as possible, optimize and simplify the Kernel, and at the same time, due to the minimal SoC system used, redundant hardware initialization code is saved. The final system startup code file Meet storage and running space requirem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com