Test chip and integration method

An integration method and chip technology, applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problems of chip/electronic device failure, open circuit, etc., and achieve the effect of improving reliability, life, and high flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] The specific implementation manners according to the present invention will be described below in conjunction with the accompanying drawings.

[0061] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, therefore, the present invention is not limited to the specific embodiments disclosed below limit.

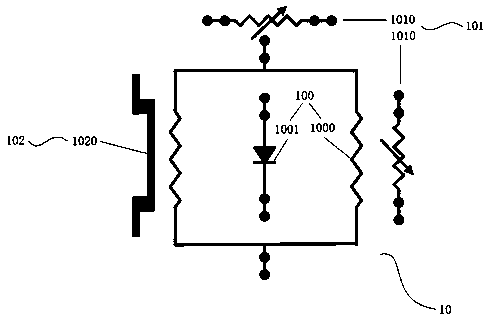

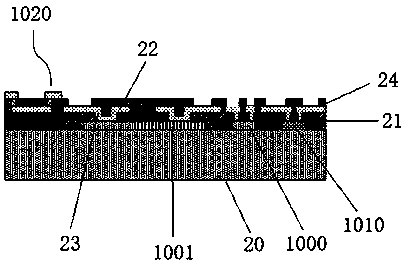

[0062] The present invention provides a test chip, for details see Figure 1 to Figure 3 , including a test unit 1, the test unit 1 is distributed in a chip (not shown in the figure) singly or in an array, the test unit 1 includes a number of basic units 10 distributed in an array, and several basic units 10 have the functions of series, parallel or both series and Parallel connection relationship; each basic unit 10 includes a thermal test module 100, a stress test module 101 and an electromigration test m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com