Capacitor mismatch error shaping switching circuit and method suitable for oversampling SAR ADC

A capacitance mismatch and oversampling technology, applied in electrical components, electrical signal transmission systems, analog/digital conversion calibration/testing, etc., can solve problems such as increased complexity, and achieve low driving force requirements, simple logic, and error shaping. good effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In the following, the present invention will be further explained in conjunction with the figures and simulation results.

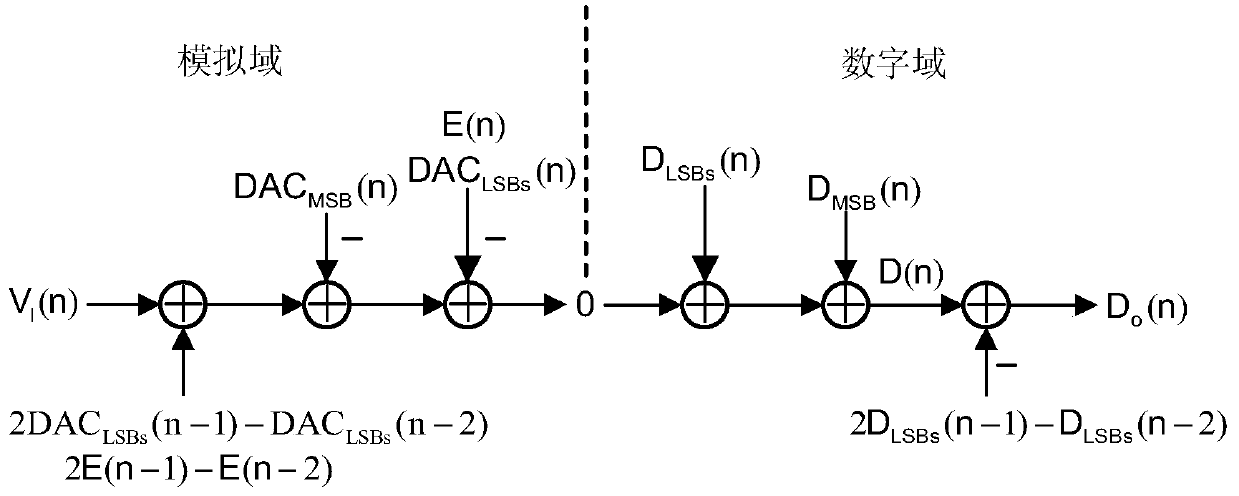

[0026] Taking the MSB DAC as a reference, first consider the case where the high-level capacitor has only 1 bit. The high-level capacitor itself can be considered as having no error, and the value of the low-level capacitor (LSB DAC) has an error relative to the MSB capacitor, which is specifically reflected in the analog domain. There is an error between the bit weight and the ideal value, so only the mismatch error of the low-level capacitor needs to be considered. In order to realize the shaping of the capacitance mismatch error, in the nth conversion, the combination of the previous two LSB DAC comparison results, 2D i (n-1)-D i (n-2), together with the mismatch error of the LSB DAC part 2E i (n-1)-E i (n-2) Feed back to the nth conversion to realize the error shaping.

[0027] figure 1 Is the behavioral model of the present invention, where E is t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com