Array substrate and preparation method thereof, and display panel

A technology for array substrates and substrate substrates, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as IGZO breakage, affecting product yield, and cracks, so as to avoid breakage and improve product preparation yield Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

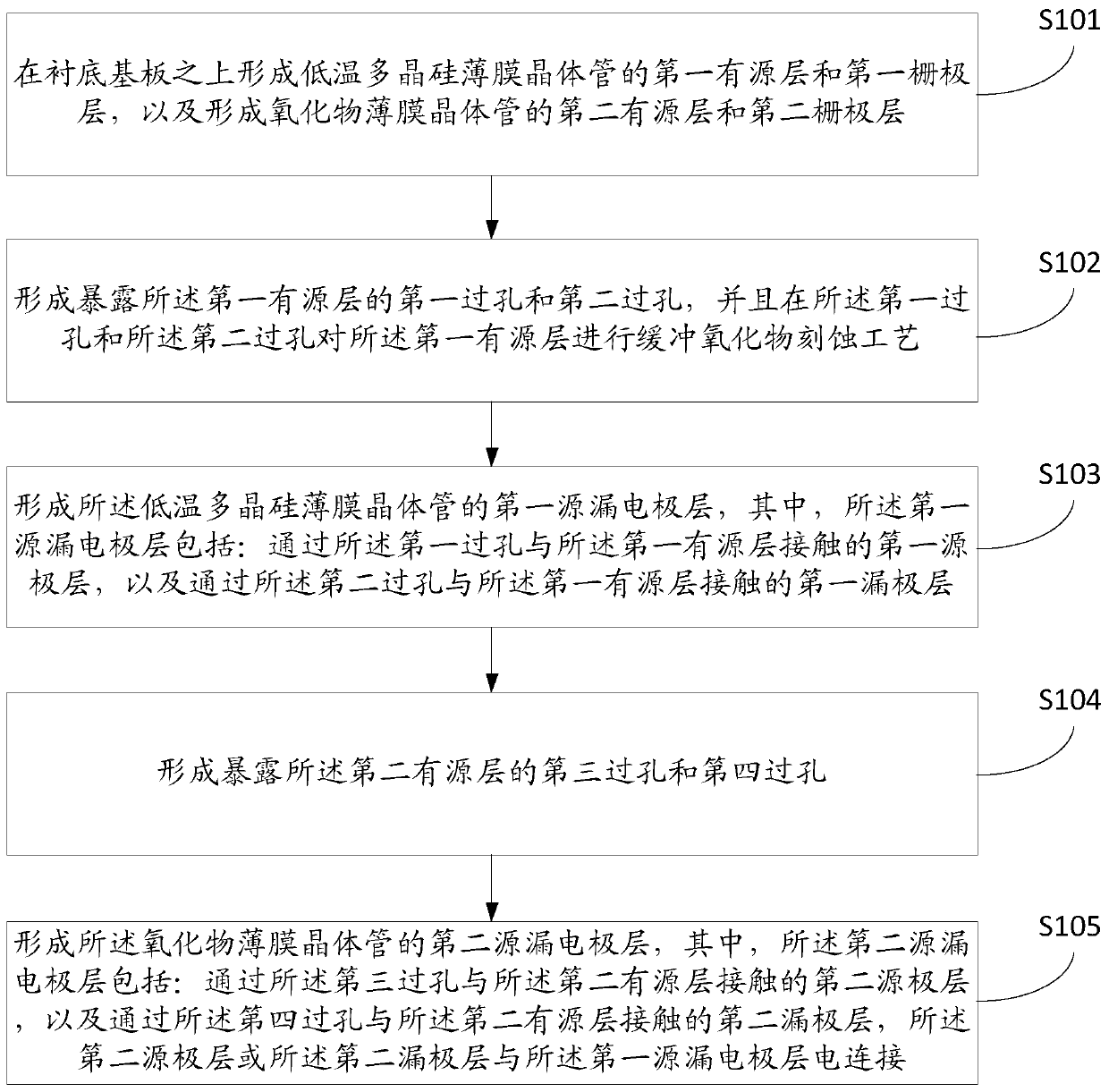

[0041] The embodiment of the present application provides a method for preparing an array substrate, such as figure 1 As shown, the method includes:

[0042] S101, forming a first active layer and a first gate layer of a low-temperature polycrystalline thin film transistor on a base substrate, and forming a second active layer and a second gate layer of an oxide thin film transistor;

[0043] S102, forming a first via hole and a second via hole exposing the first active layer, and performing buffer oxide etching on the first active layer in the first via hole and the second via hole etching process;

[0044] S103. Form the first source-drain electrode layer of the low-temperature polysilicon thin film transistor, wherein the first source-drain electrode layer includes: a first source contacting the first active layer through the first via hole layer, and a first drain layer in contact with the first active layer through the second via hole;

[0045] S104, forming a third vi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com