Layout correction method

A technology of layout and graphics, applied in the field of layout correction, can solve the problems of actual graphics distortion, disconnection, uneven distribution of light energy, etc., and achieve the effect of ensuring no distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

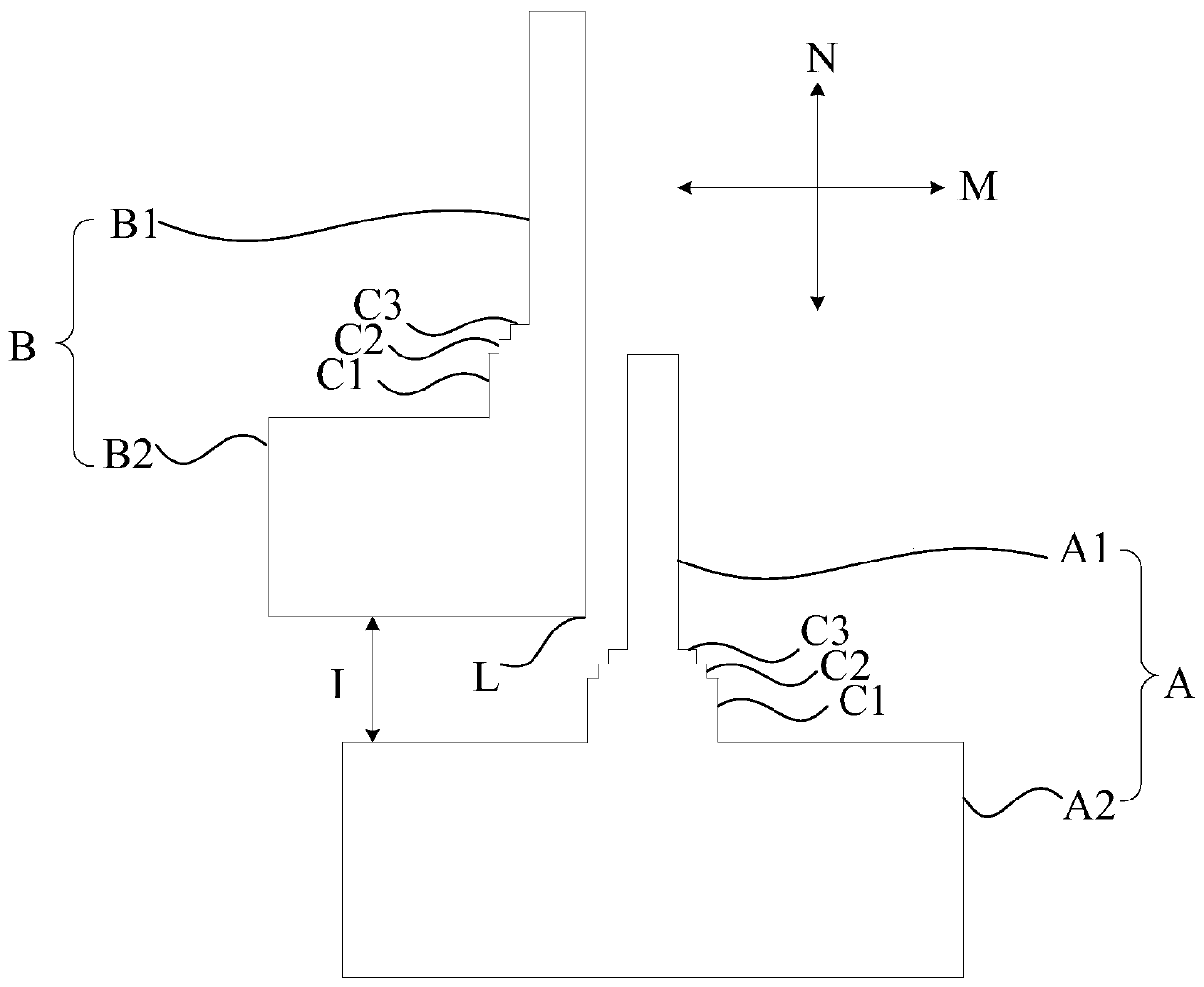

[0037] The layout correction method proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that the drawings are all in a very simplified form and use inaccurate scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0038] figure 2 A schematic flowchart of a layout correction method provided by an embodiment of the present invention, as shown in Figure 2, the method may include:

[0039] Step 100, obtaining the original layout.

[0040]The original layout may include at least two target patterns, the target pattern includes a first graphic and a second graphic, the first graphic may be a bar structure, and the first graphic and the second graphic are connected One or both sides of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com