A fpga-based nvme SSD PCIe packet analysis method

A parsing method and data packet technology, applied in the field of FPGA-based NVMeSSDPCIe packet parsing, can solve problems such as many logic resources and complex PCIe packet parsing process, and achieve the effect of saving logical resources, complete functions, and simplifying parsing process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

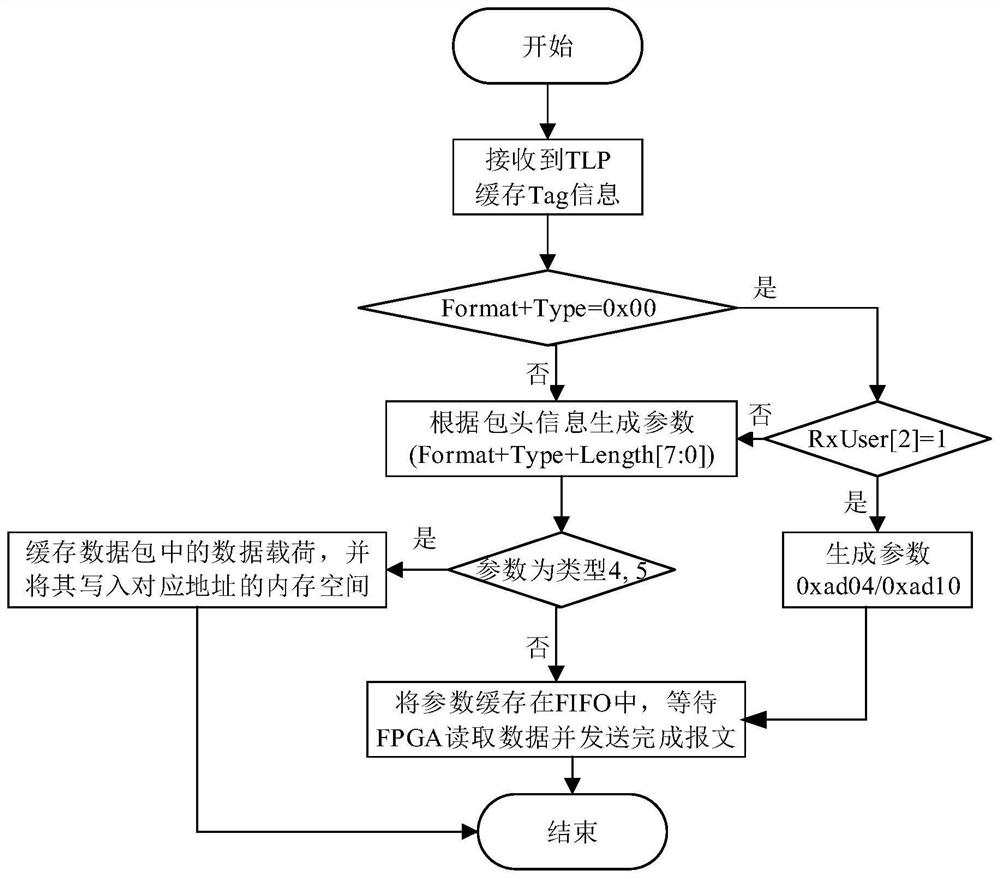

[0026] Specific embodiment one: a kind of FPGA-based NVMe SSD PCIe data packet analysis method described in this embodiment, the TLP (transaction layer data packet) that needs to analyze in the described FPGA-based NVMe SSD PCIe data packet analysis method includes reading memory (Memory Read) TLP and write memory (Memory Write) TLP; and for each TLP, its corresponding format (Format) information, type (Type) information and length (Length) information need to be parsed;

[0027] Wherein: the format information and the type information are used to determine the type of the corresponding TLP, and the length information is used to determine the function of the corresponding TLP;

[0028] The TLP parameter of each TLP is a 16-bit binary number, the upper 8 bits of the TLP parameter are the format information and type information of the corresponding TLP, and the lower 8 bits of the TLP parameter are the lower 8 bits of the length information of the corresponding TLP.

[0029] The...

specific Embodiment approach 2

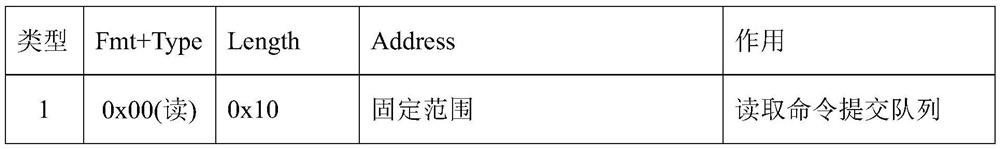

[0041] Embodiment 2: The difference between this embodiment and Embodiment 1 is that the TLP parameters include 5 types; the TLP parameters of Type 1 are expressed as 0x0010, the TLP parameters of Type 2 are expressed as 0x0010 or 0x0004, and the TLP parameters of Type 3 are expressed as 0x0010 or 0x0004. The parameter is represented as 0x0040, the TLP parameter of type 4 is represented as 0x4020, and the TLP parameter of type 5 is represented as 0x4004.

[0042] Each type of TLP parameter in this embodiment is generated by combining the lower 8-bit information of the format, type and length.

specific Embodiment approach 3

[0043] Embodiment 3: This embodiment is different from Embodiment 2 in that: the type 2 TLP parameter representation is replaced with 0xad04 / 0xad10, and 0xad04 / 0xad10 is used to distinguish it from the type 1 TLP parameter.

[0044] The present invention defines "TLP parameters" as follows:

[0045] (1) The parameter is a 16-bit binary number;

[0046] (2) The upper 8 bits of the parameter are the Fmt+Type of the TLP, and the lower 8 bits of the parameter are the Length[7:0] of the TLP;

[0047] (3) The TLP parameter of special definition type 2 is 0xad04 / 0xad10.

[0048] The present invention has carried out special definition to the TLP parameter of type 2, and its reason is as follows: TLP type 1, 3, 4 and 5 correspond to a kind of TLP parameter respectively, and type 2 corresponds to two kinds of Fmt+Type+Length parameters, wherein a kind of parameter 0x0010 is the same as the TLP parameter of type 1.

[0049] In order to simplify the parsing process, the present invent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com