Device and method for testing performance of semiconductor chip

A chip performance, semiconductor technology, applied in the field of communication, can solve the problems of uncontrollable pressure, inapplicability, chip damage, etc., to achieve the effects of low device cost, high operating efficiency, and simple operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

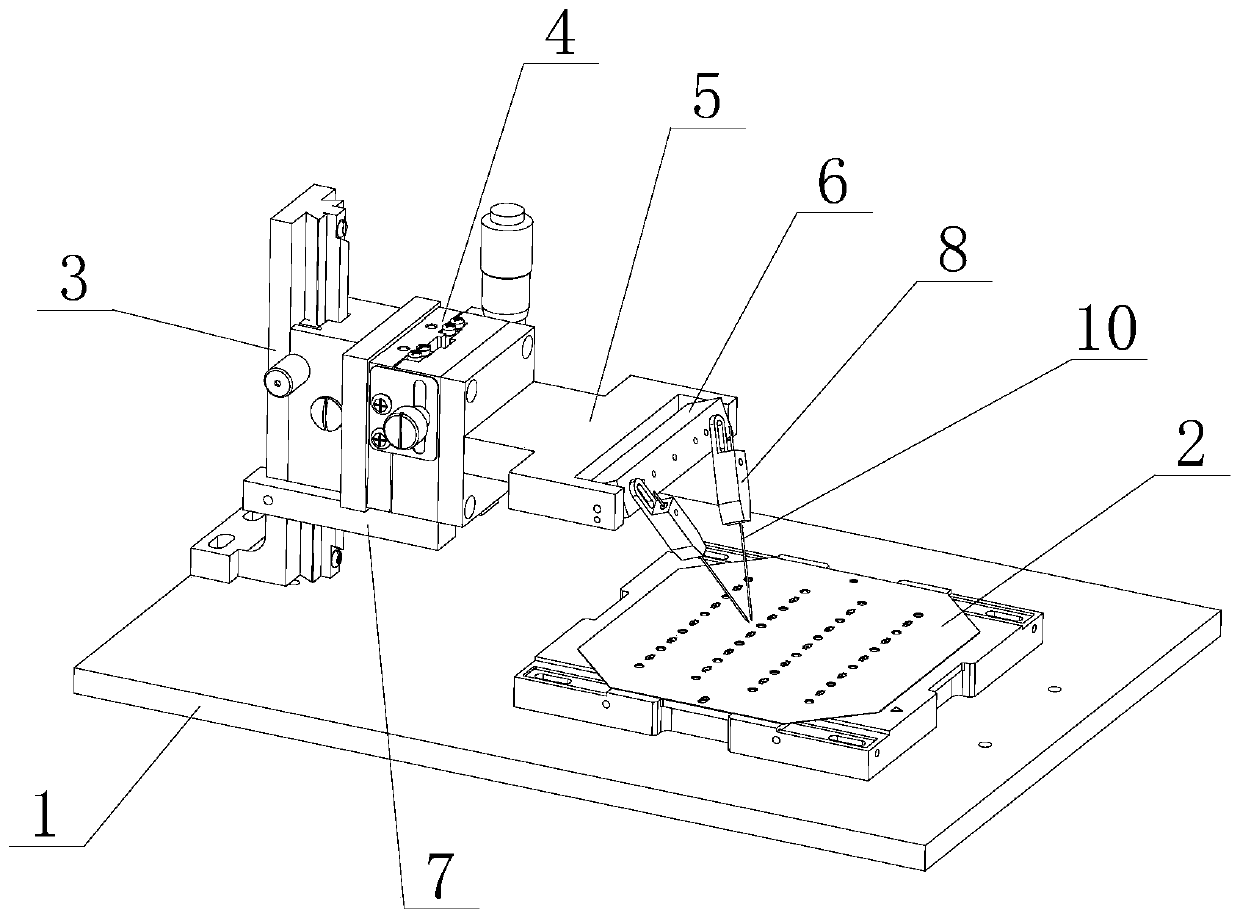

[0029] The present invention is described in further detail now in conjunction with accompanying drawing. These drawings are all simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so they only show the configurations related to the present invention.

[0030] like Figure 1-2 As shown, a device for performance testing of semiconductor chips includes a base plate 1, an adjustment assembly, a probe assembly and a carrier plate 2. The adjustment assembly and the carrier plate 2 are respectively arranged on the left and right sides of the base plate 1, and the probe assembly is arranged Above the carrier plate 2, the probe assembly is detachably connected to the adjustment assembly;

[0031] The adjustment assembly includes a quick adjustment frame 3, a fine-tuning adjustment frame 4, a mechanical arm 5 and an angle shaft 6, the quick adjustment frame 3 is vertically installed on the base plate 1, and the fine-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com