Common-mode voltage suppression method and system for unbalanced npc three-level inverter on DC side

A three-level inverter and common-mode voltage technology, which is applied in the direction of converting AC power input to DC power output, electrical components, output power conversion devices, etc., can solve the problems of slow modulation efficiency, poor suppression of common-mode voltage, Problems such as slow dynamic response speed, to achieve fast dynamic response speed, common mode voltage suppression, and elimination of even harmonics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

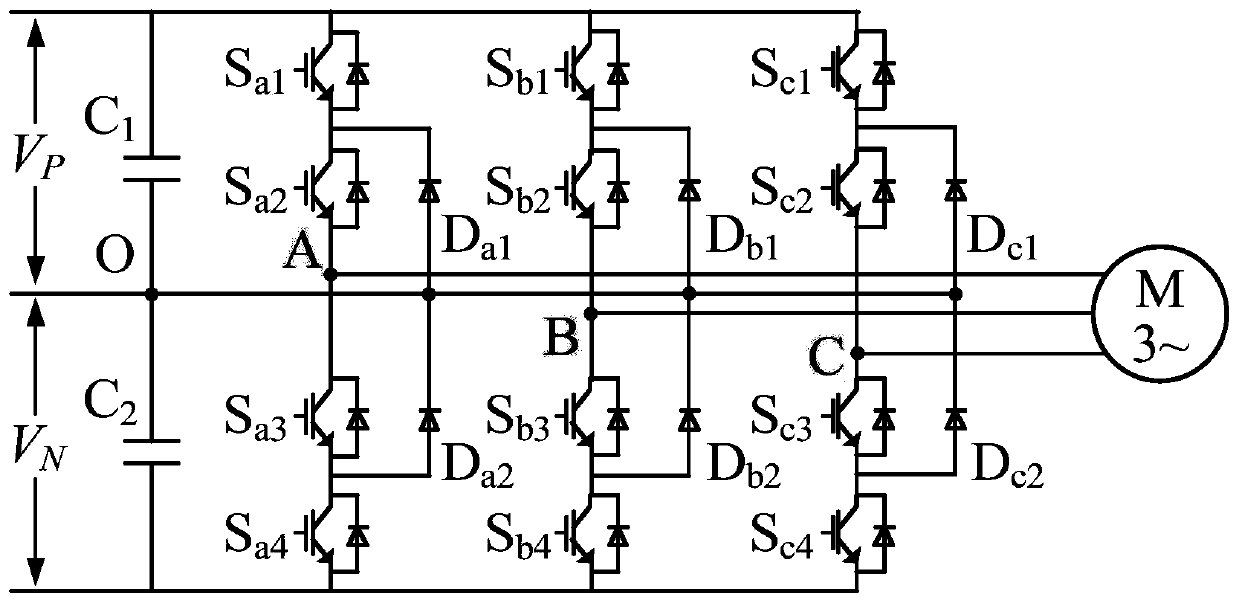

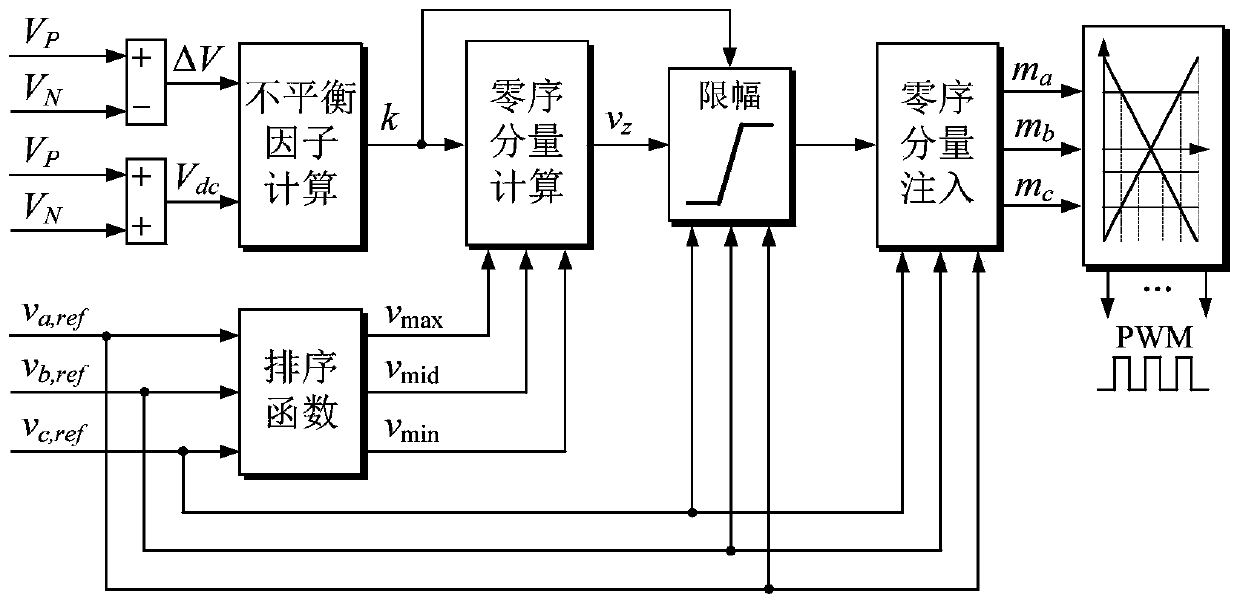

[0053] figure 2It shows that the front ends of the two capacitors on the DC side of the NPC three-level inverter are respectively connected to a group of diode uncontrolled rectifiers. At this time, the voltages of the two capacitors will be unequal. In order to suppress the common mode voltage in the case of unbalanced capacitor voltage on the DC side, and at the same time ensure low harmonic three-phase output current.

[0054] The zero-sequence component expression of Embodiment 1 is

[0055]

[0056] In order to avoid the basic voltage vector of high common-mode voltage amplitude caused by over-modulation causing output waveform distortion and carrier modulation, it is necessary to zero-sequence component v of the first embodiment z clipping

[0057] max{v za,min ,v zb,min ,v zc,min}≤v z ≤min{v za,max ,v zb,max ,v zc,max}(8)

[0058] in,

[0059]

[0060]

[0061] j = a, b, c.

[0062] The zero-sequence component v z1 Inject a three-phase modulating ...

Embodiment 2

[0070] Figure 6 It is shown that the front ends of the two capacitors on the DC side of the NPC three-level inverter are connected to a group of diode uncontrolled rectifiers. At this time, according to the requirements of the actual system, the voltage difference between the two capacitors can be equal to its corresponding voltage by means of control. Desired point.

[0071] Let the given value of the voltage difference between the two capacitors on the DC side be Δv ref , design the deadbeat midpoint potential control algorithm, and get the given value of the midpoint current

[0072]

[0073] In the case of unbalanced DC side, the expression of the midpoint current of the NPC three-level inverter system is

[0074]

[0075] Among them, n j is the switch state transition function of phase j (j=a,b,c) of the NPC three-level inverter system, defined as

[0076]

[0077] In order to realize that the voltage difference between the two capacitors is equal to its cor...

Embodiment 3

[0098] This embodiment provides a computer-readable storage medium, on which a computer program is stored, and when the program is executed by a processor, the DC-side unbalanced NPC three-level inverter as described in Embodiment 1 or Embodiment 2 is realized. steps in the common-mode voltage rejection method.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com