Tag storage bit readout comparison circuit and tag data readout comparison circuit

A comparison circuit and tag storage technology, which is applied in the circuit field, can solve the problems that the speed of the tag storage bit readout comparison circuit needs to be improved, and achieve the effects of improving the readout and comparison speed, reducing error interference, and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] As described in the background art, the readout and comparison speed of the existing tag memory needs to be improved.

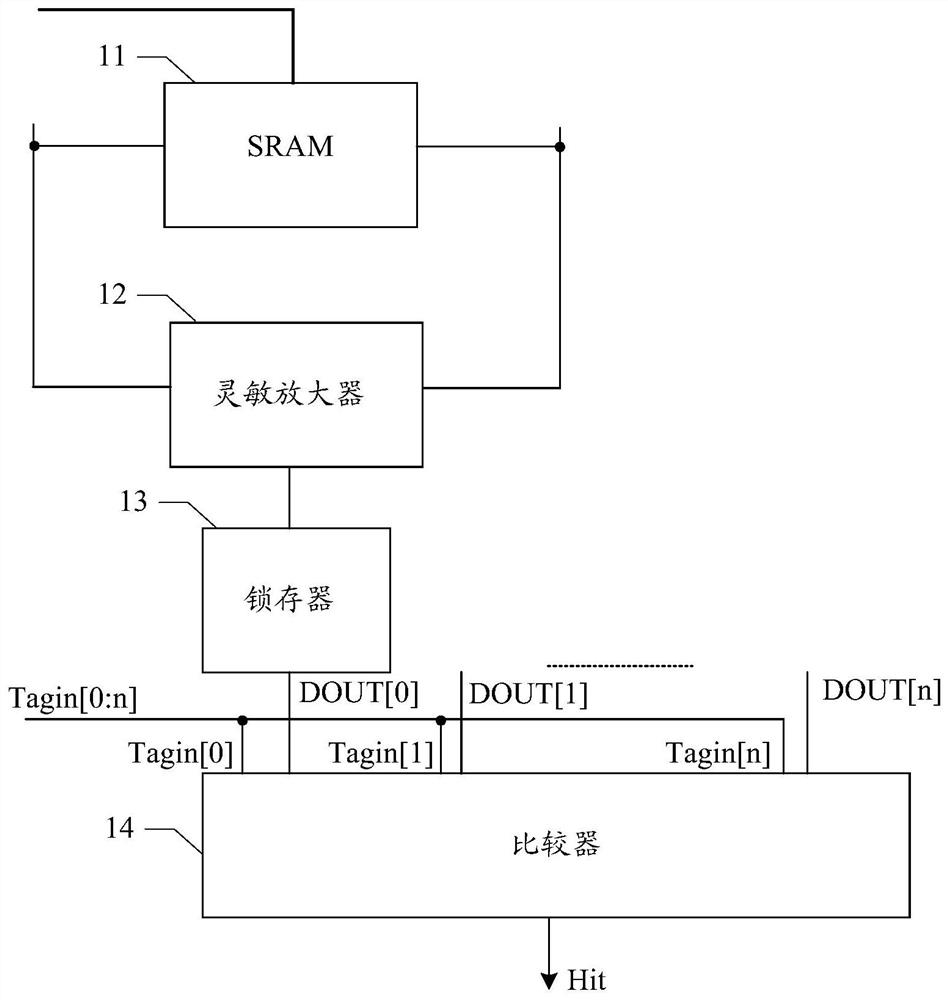

[0040] figure 1 It is a schematic diagram of the structure of a tag storage bit readout comparison circuit. In the reading and comparison of the data of the tag storage bit, it is first necessary to read the tag data from the Static Random-Access Memory (SRAM) 11, and the address bit signal obtained by reading the tag data passes through the bit line The sensitive amplifier 12 is connected, and the address bit amplified signal outputted by the sensitive amplifier 12 is latched by the latch 13. The address bit amplifying signal DOUT output by the latch 13 is connected to the comparator 14 and compared with the target address bit signal Tagin of the externally connected target tag data. The comparator 14 compares the address bit amplifying signal DOUT and the target address bit signal Tagin The comparison result signal Hit is output.

[0041] Among them, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com