FPGA-based graph data processing method and system

A processing method and technology of graph data, applied in the field of FPGA graph computing, can solve problems such as time-consuming, long-tail effect, cumbersome and complex, etc., and achieve the effect of avoiding control operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

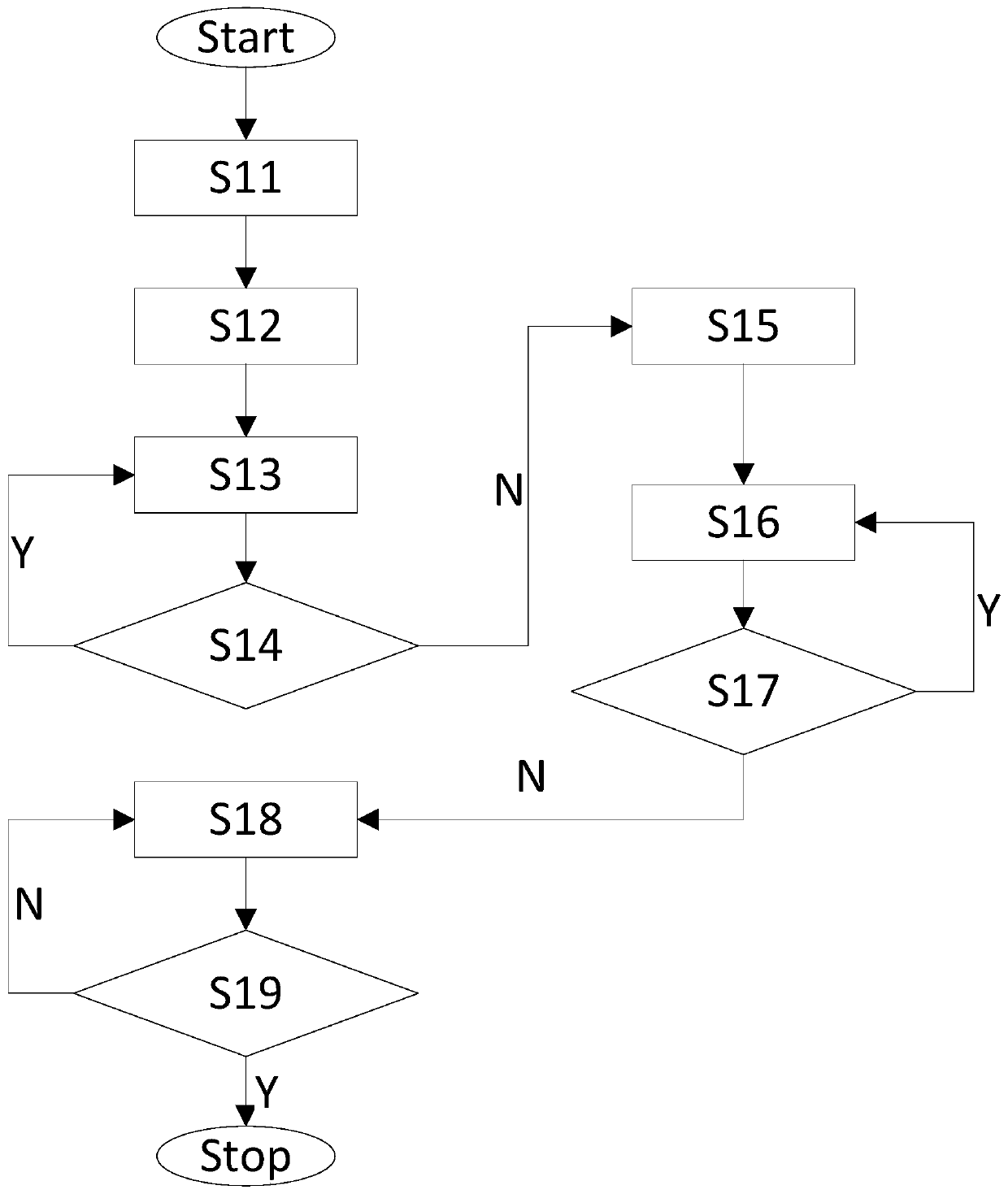

[0044] According to one aspect of the present invention, the present invention discloses an FPGA-based graph data processing method, or a graph data processing method, or a graph data processing method. The method may be implemented by the system of the present invention and / or other alternative components. In the case of no conflict or contradiction, the whole and / or part of the content of the preferred implementations of other embodiments may serve as supplements to this embodiment.

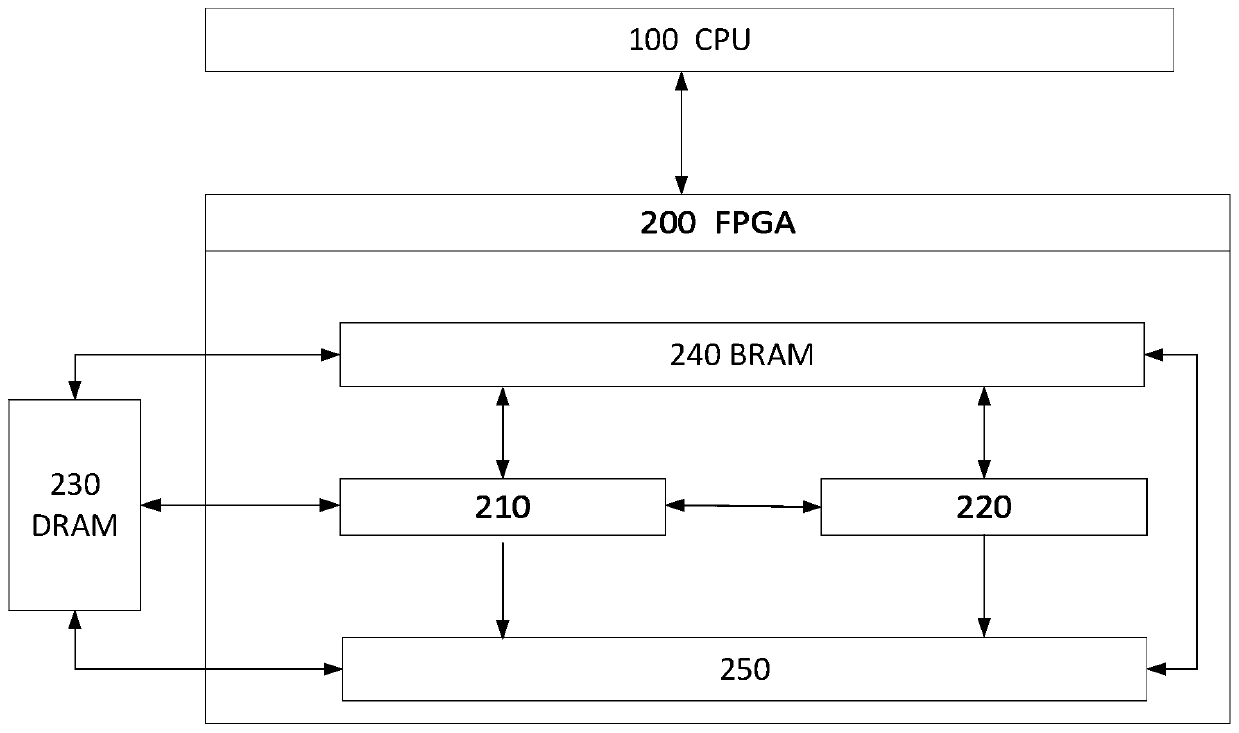

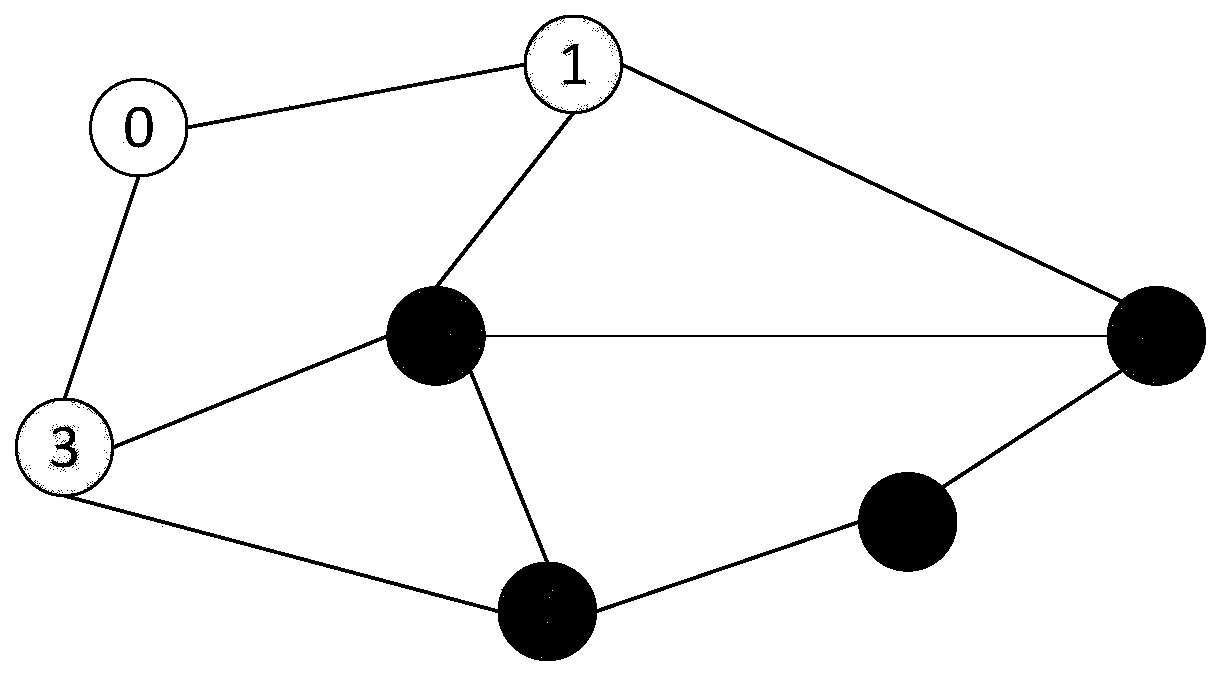

[0045] According to a preferred embodiment, see figure 1 , this method can be used for graph traversal of graphs with small-world network properties. Preferably, the method may include: using a first processor 100 and a second processor 200 communicatively connected to the first processor 100 . The method may include: using the first processor 100 and / or the second processor 200 communicatively connected to the first processor 100 to perform graph traversal. The first processor 100 may be a ...

Embodiment 2

[0093] According to another aspect of the present invention, the present invention discloses an FPGA-based graph traversal system, which is suitable for executing each method step described in the present invention to achieve expected technical effects.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com