PCIe pressure eye pattern test calibration method

An eye diagram and stress technology, applied in the computer field, can solve the problems of insufficient signal-to-noise ratio and calibration failure of oscilloscope, and achieve the effect of solving the problem of insufficient signal-to-noise ratio, enhancing flexibility and saving calibration time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0042] The embodiment of the present invention is to test and calibrate the receiver stress eye diagram at the PCIe3.0 8G rate chip end, and use seasim software for simulation. Specific implementation steps:

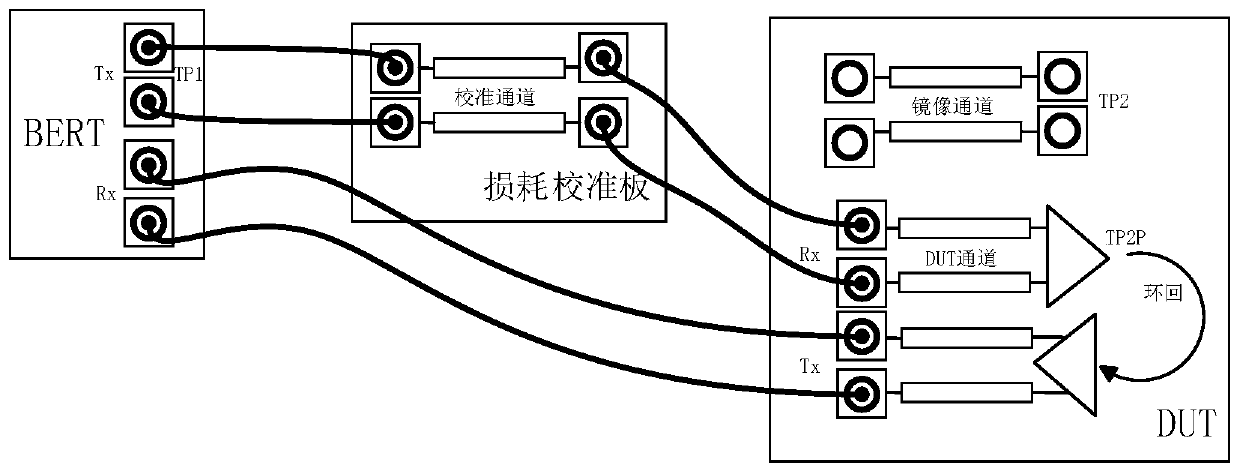

[0043] 1. Use a network analyzer to test the loss from the signal input point of the loss calibration board to the output point of the image channel on the device under test, and ensure that the IL is within 20dB+ / -2dB, and save the test results as an S parameter file for later simulation.

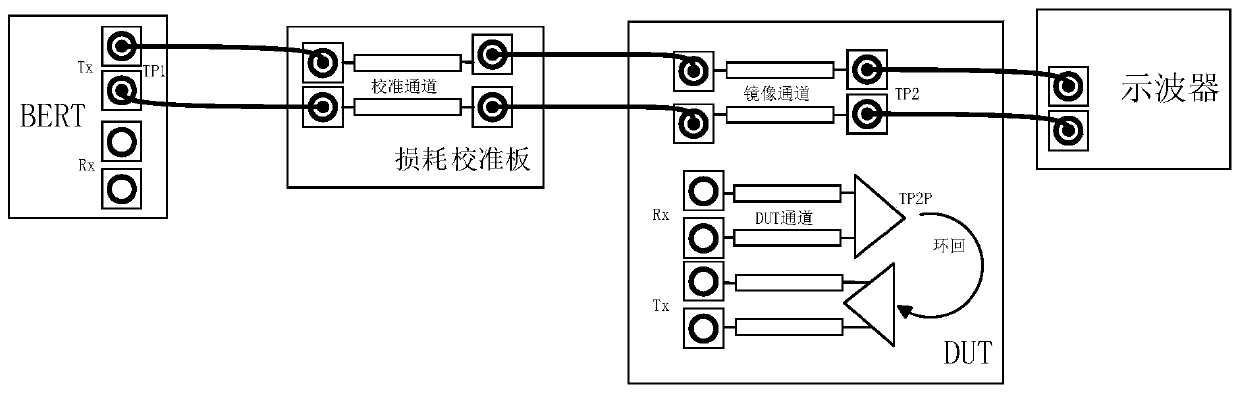

[0044] 2. Preheat BERT and oscilloscope until the temperature of the instrument is stable. Record the noise floor V of the oscilloscope test results at this time nosc .

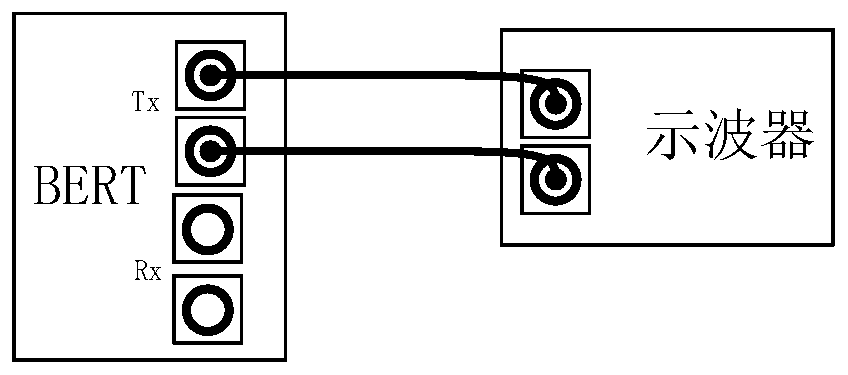

[0045] 3. Connect BERT directly to the oscilloscope, such as image 3 As shown, use the automatic calibration program that comes with BERT to calibrate the accuracy and linearity of SJ, RJ, and DM-SI, connect the oscilloscope directly to the oscilloscope, and use the calibration program that comes with BERT to co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com