Dynamic binary translation method and device for vliw architecture

A dynamic binary and translation device technology, applied in the computer field, can solve the problems of low performance of VLIW programs, and achieve the effects of reducing overhead, ensuring correctness, and improving execution performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments. It should be pointed out that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0027] VLIW (Very Long Instruction Word, Very Long Instruction Word) is a microprocessor architecture that allows multiple instructions to be arranged in a very long (128--1024 bits) very long instruction word and enters the pipeline for execution. A single operation of a VLIW architecture microprocessor has a definite execution cycle, and the correctness of the program is realized by the compiler scheduling.

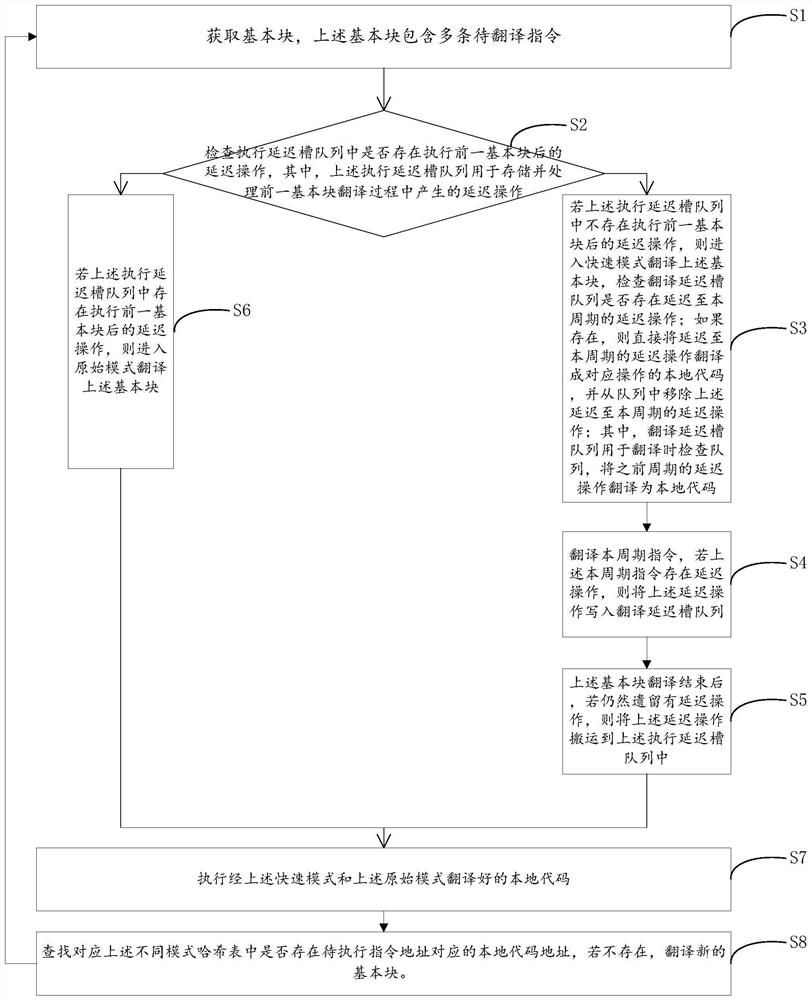

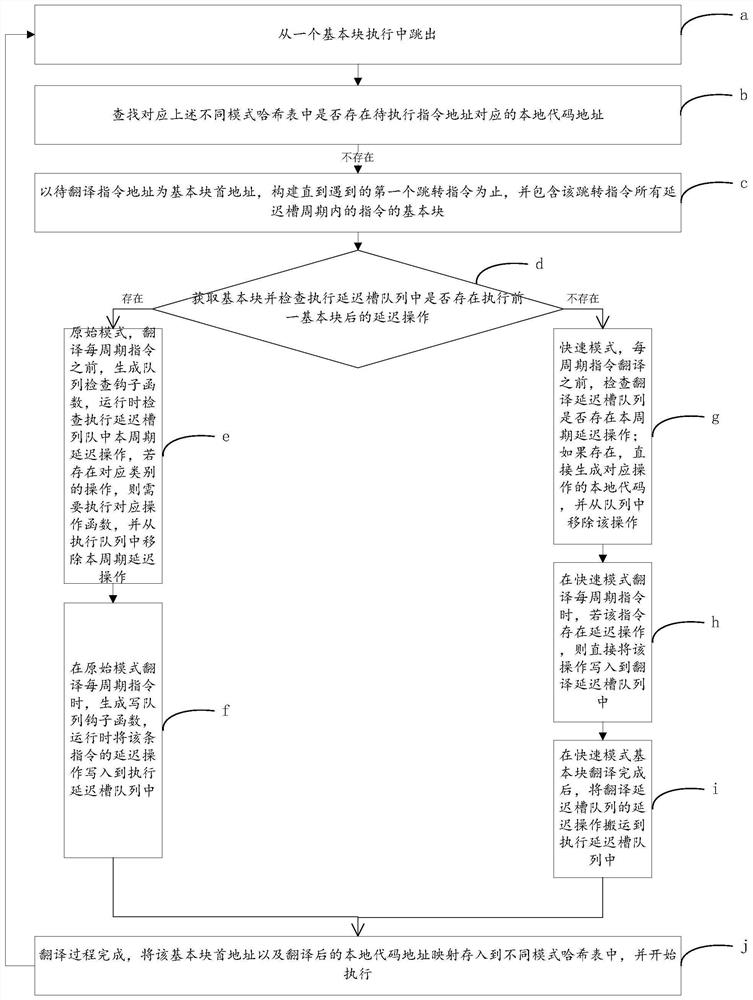

[0028] figure 1 It is the process flow of the dynamic binary translation method according to an optional embodiment of the present invention Figure 1 ,Such asfigure 1 As shown, the method includes the following steps:

[0029] Step S1: Obtain a basic block, which co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com