Emitter structure of double-layer amorphous silicon doped layer solar cell and preparation method thereof

A technology for solar cells and amorphous silicon layers, applied in circuits, photovoltaic power generation, electrical components, etc., can solve problems such as low transmittance, inability to achieve high conversion efficiency of HJT cells, poor conductivity, etc., to increase conductivity, The effect of improving photoelectric conversion efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

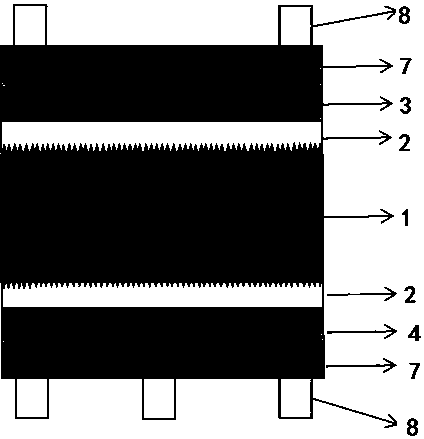

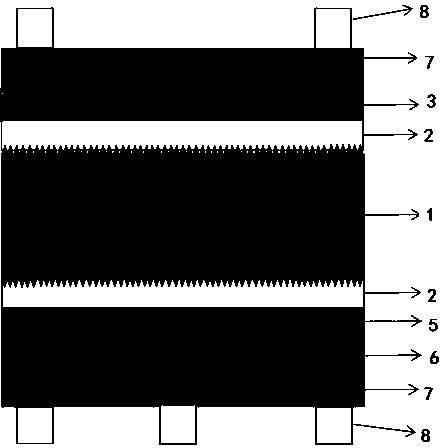

[0032] see figure 2 , the emitter structure of a double-layer amorphous silicon doped layer solar cell related to the present invention, it includes an N-type crystalline silicon wafer 1, and the front and back sides of the N-type crystalline silicon wafer 1 are provided with amorphous silicon substrates. Levy layer 2;

[0033] The outside of the amorphous silicon intrinsic layer 2 on the front is provided with an amorphous silicon doped layer N layer 3, and the outside of the front amorphous silicon doped layer N layer 3 is provided with a TCO conductive film 7, and the TCO Several Ag electrodes 8 are provided on the outside of the conductive film 7;

[0034] The outside of the amorphous silicon intrinsic layer 2 on the back is provided with a first doped layer 5, and the outside of the first doped layer 5 is provided with a second doped layer 6, and the second doped layer A TCO conductive film 7 is provided on the outside of the heterogeneous layer 6 , and several Ag elec...

Embodiment 2

[0047] see figure 2 , the emitter structure of a double-layer amorphous silicon doped layer solar cell that the present invention relates to comprises an N-type crystalline silicon chip 1, and the front and back sides of the N-type crystalline silicon chip 1 are provided with amorphous silicon substrates. Levy layer 2;

[0048] The outside of the amorphous silicon intrinsic layer 2 on the front is provided with an amorphous silicon doped layer N layer 3, and the outside of the front amorphous silicon doped layer N layer 3 is provided with a TCO conductive film 7, and the TCO Several Ag electrodes 8 are provided on the outside of the conductive film 7;

[0049] The outside of the amorphous silicon intrinsic layer 2 on the back is provided with a first doped layer 5, and the outside of the first doped layer 5 is provided with a second doped layer 6, and the second doped layer A TCO conductive film 7 is provided on the outside of the heterogeneous layer 6 , and several Ag elec...

Embodiment 3

[0062] see figure 2 , the emitter structure of a double-layer amorphous silicon doped layer solar cell related to the present invention, it includes an N-type crystalline silicon wafer 1, and the front and back sides of the N-type crystalline silicon wafer 1 are provided with amorphous silicon substrates. Levy layer 2;

[0063] The outside of the amorphous silicon intrinsic layer 2 on the front is provided with an amorphous silicon doped layer N layer 3, and the outside of the front amorphous silicon doped layer N layer 3 is provided with a TCO conductive film 7, and the TCO Several Ag electrodes 8 are provided on the outside of the conductive film 7;

[0064] The outside of the amorphous silicon intrinsic layer 2 on the back is provided with a first doped layer 5, and the outside of the first doped layer 5 is provided with a second doped layer 6, and the second doped layer A TCO conductive film 7 is provided on the outside of the heterogeneous layer 6 , and several Ag elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com