Digital Accurate Delay Matching Circuit

A matching circuit and digital technology, applied in the field of digital precise time delay matching circuit, can solve the problems of high pass frequency band, cannot be realized at the same time, limited adjustable accuracy, etc., achieves good versatility, high delay adjustment accuracy, Effects with a wide range of delay adjustments

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments, so as to facilitate a clear understanding of the present invention, but they do not limit the present invention.

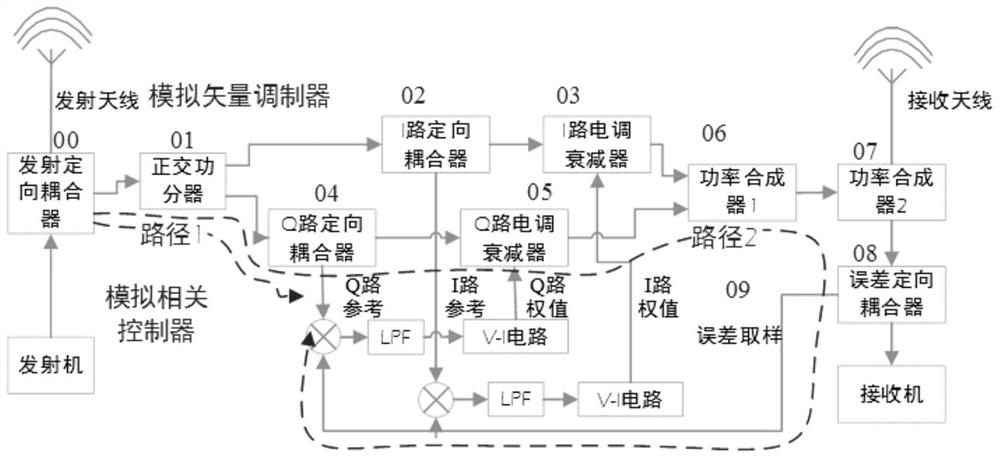

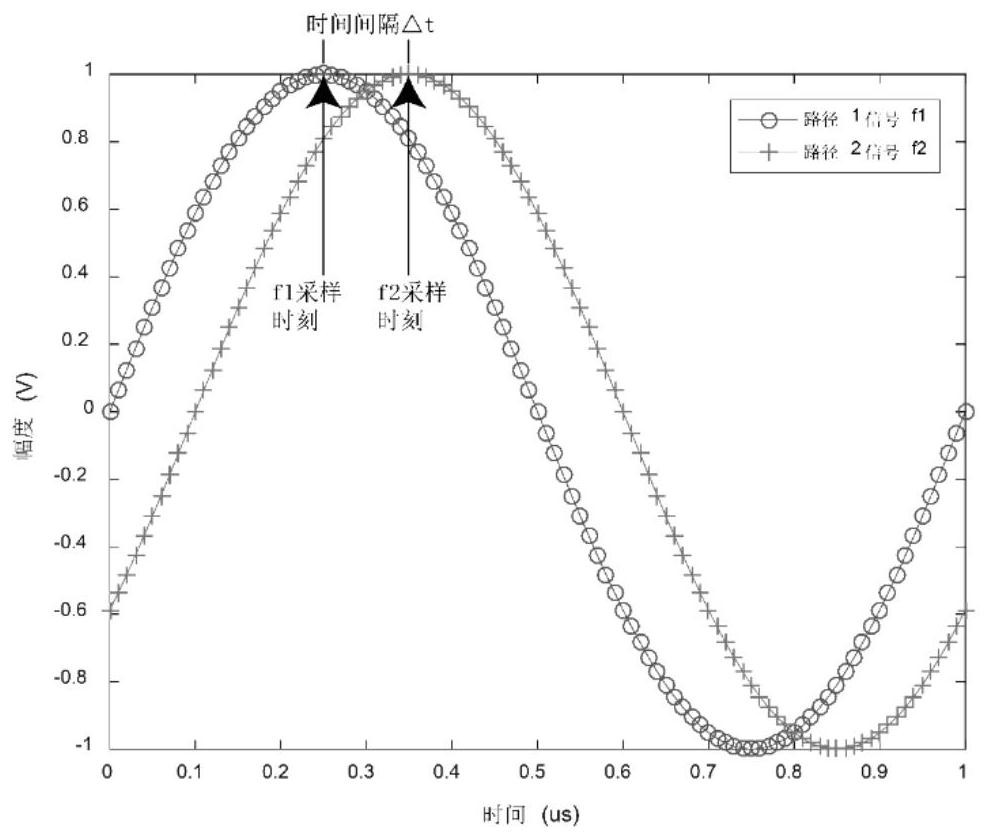

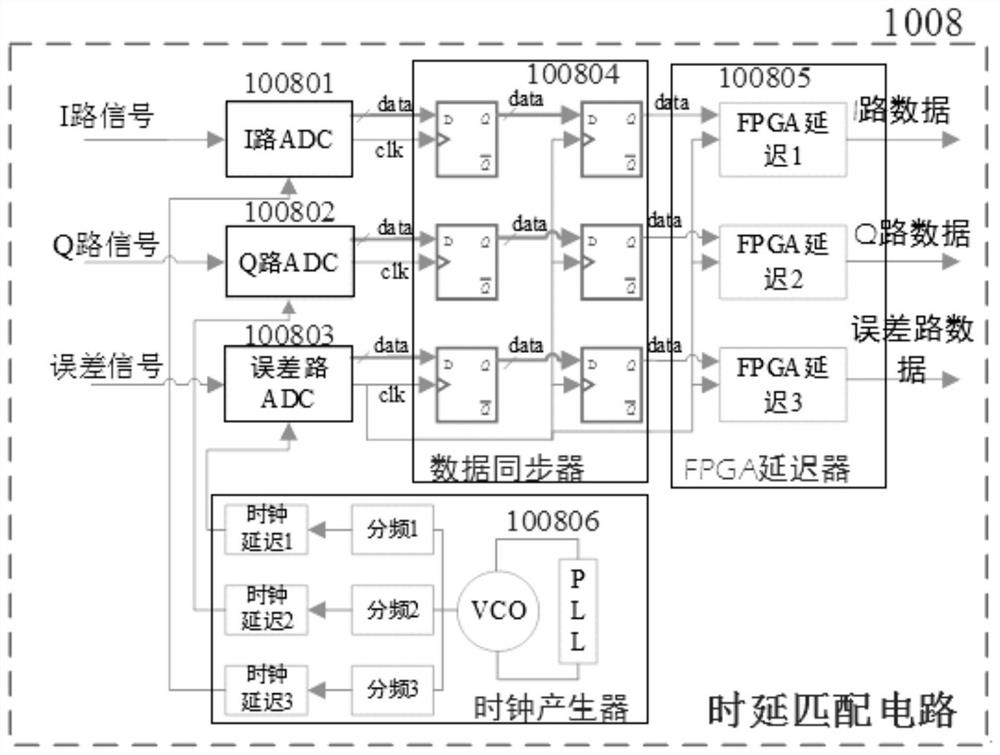

[0019] figure 1 A block diagram of a general adaptive interference cancellation device is shown, which consists of an analog vector modulator and an analog correlation controller. The analog vector modulator completes the extraction, decomposition, adjustment, synthesis and error signal extraction of the reference signal, and the analog correlation controller completes the correlation multiplication and low-pass filter of the signal. Delay matching means that the phase of the reference signal when it reaches both ends of the analog multiplier after passing through path 1 and path 2 is still the same. Path 1 includes quadrature power divider 01, Q-way directional coupler 04 coupling output, path 2 includes quadrature power di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com