Accelerator interface

An accelerator and interface technology, applied in the field of accelerator interface, can solve the problems of low applicability, low transmission rate, high delay, and achieve the effect of strong applicability, low delay and high bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

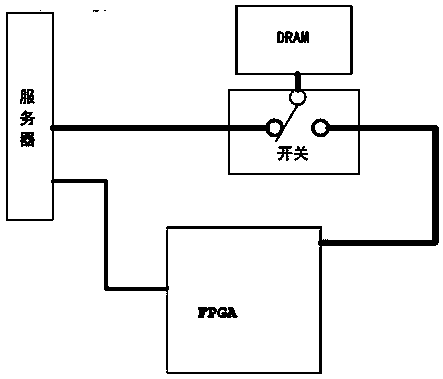

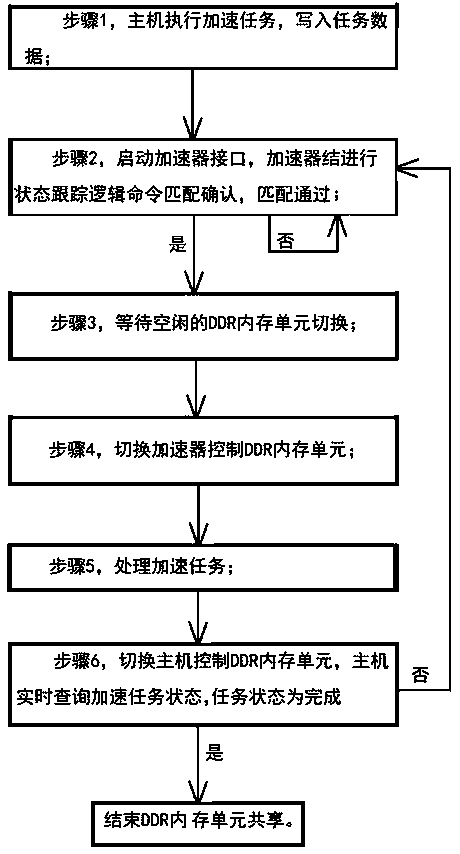

[0032] This embodiment provides an accelerator interface, such as figure 1 , the accelerator interface is connected between the server and the accelerator; the accelerator interface is a DDR interface, the DDR interface includes a DDR storage module, and a high-speed switch for controlling the sharing or disconnection of the DDR memory unit, and the accelerator interface adopts the DDR address and The command signal sequence completes the data communication between the server and the accelerator.

[0033] The accelerator of this embodiment adopts FPGA, and DDR memory unit replaces DRAM. The rest are similar to this embodiment and will not be described again. DDR interface can adopt DDR3 or DDR4.

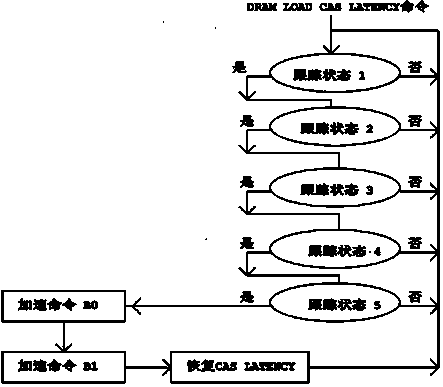

[0034] Since the DDR interface does not have an interrupt interaction mechanism, this embodiment uses a DDR address and a special sequence of command signals to communicate between the server and the accelerator. This special sequence uses the unique sequence set by CAS LATENCY in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com