Packaging method of three-dimensional heterostructure for realizing heat dissipation of high power GaN device layer

A technology of heterogeneous structure and packaging method, which is applied in the fields of electrical solid-state devices, semiconductor devices, semiconductor/solid-state device manufacturing, etc. Power GaN chip three-dimensional integrated packaging heat flux and other issues, to achieve high manufacturability, efficient heat dissipation efficiency, and high stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

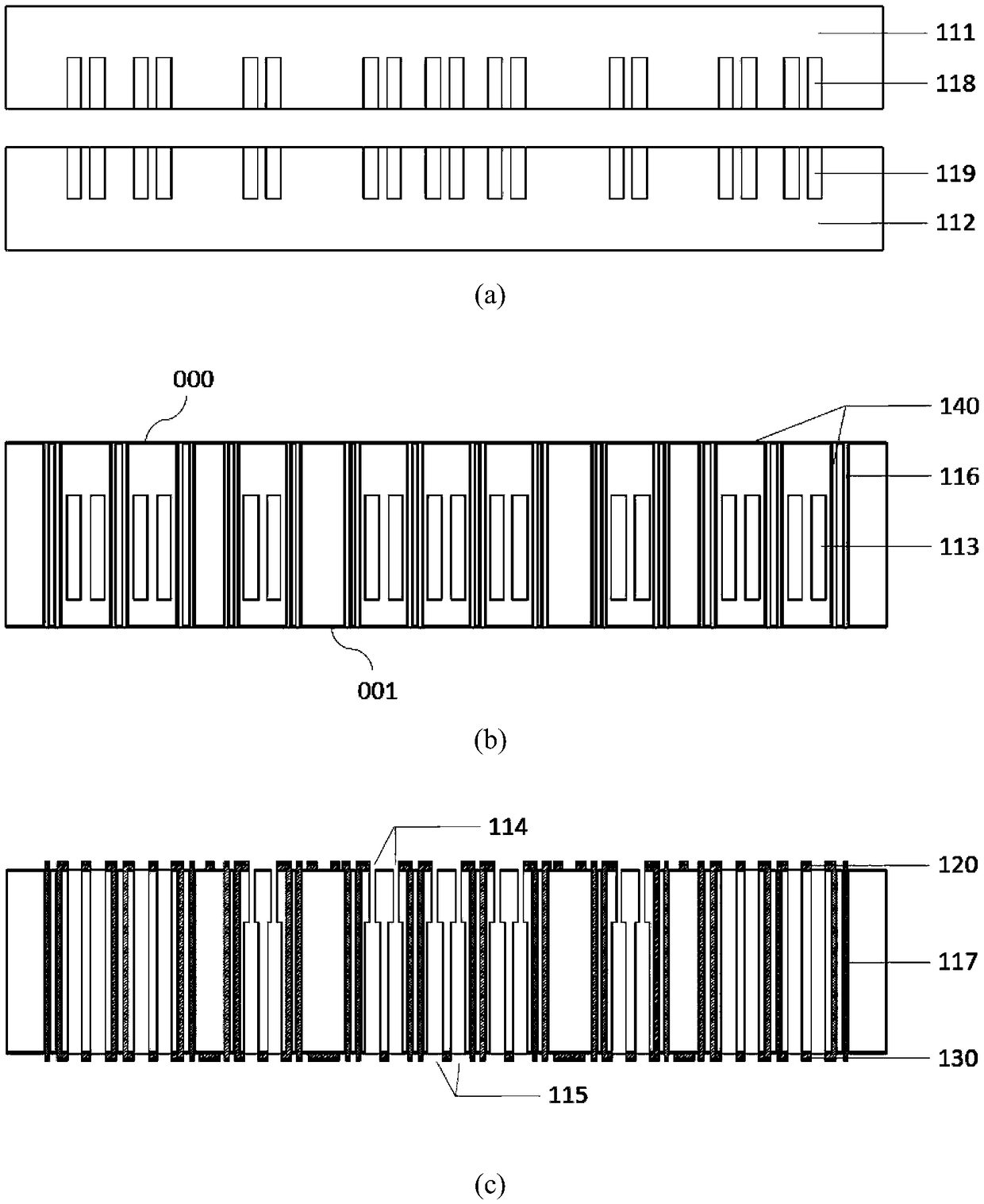

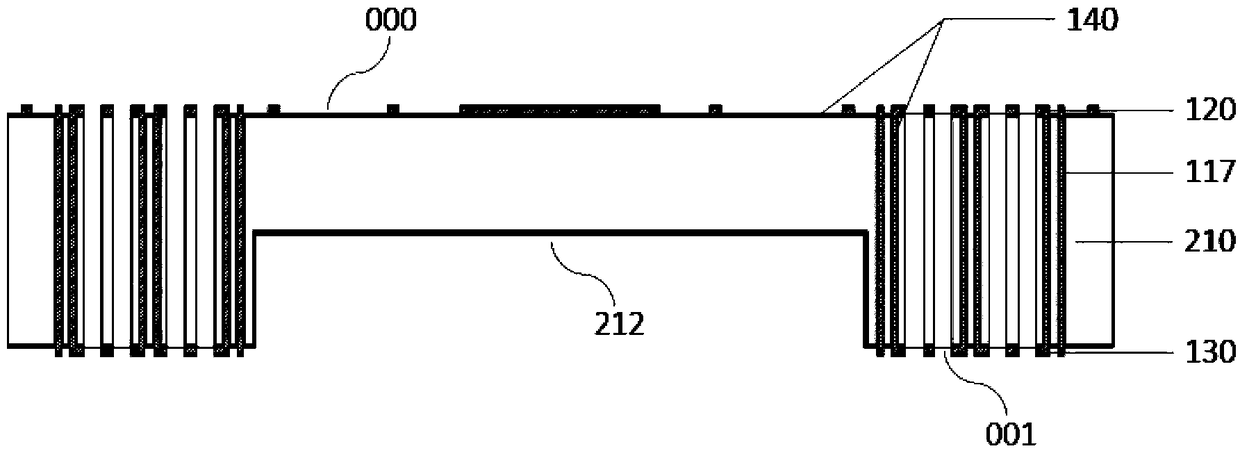

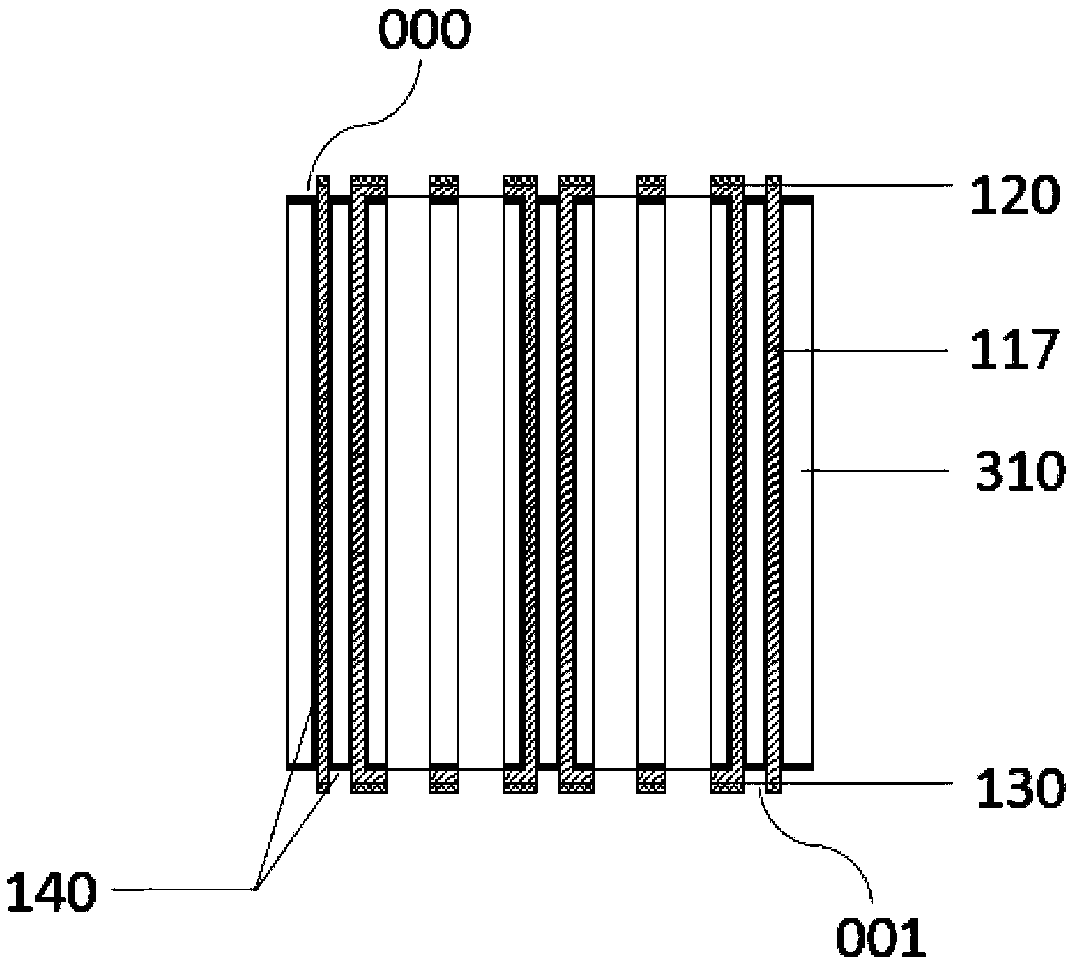

[0044] A packaging structure of a three-dimensional heterogeneous structure that realizes heat dissipation of high-power GaN device layers, such as Figure 4-6 shown, including:

[0045] The first substrate 110, the first substrate 110 made of a high-resistance silicon material (≥1000Ω·cm) substrate is composed of a first substrate 111 and a second substrate 112, and the first substrate 110 has a front surface 000 and A back surface 001, the first substrate 110 includes a certain depth of first vertical micro-channels 113 and vertical interconnection structures. The front 000 of the first substrate 110 is provided with a microchannel output port 114 corresponding to the size of the embedded microchannel structure, and the back 001 is provided with a microchannel input port 115 corresponding to the size of the embedded microchannel structure 113; The vertical interconnection structure is formed by the following structure: the first substrate 110 is provided with a plurality of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com