Flash memory chip testing method and system

A technology of flash memory chips and testing methods, applied in static memory, instruments, etc., can solve problems such as reducing measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0085] refer to Figure 4 , shows a flow chart of the flash memory chip testing method in Embodiment 1 of the present invention, which may specifically include the following steps:

[0086] Step 101, the PMU measurement unit receives a first output instruction sent by the PC; wherein, the first output instruction includes: a first output voltage instruction or a first output current instruction.

[0087] In the embodiment of the present invention, the PMU measurement unit is connected to a PC, and the PC is used to control the PMU measurement unit. The user may input the first output instruction according to a preset format on the PC, wherein the first output instruction may indicate the output voltage value or the output current value of the PMU measurement unit. At the same time, the output instruction may also include: the change speed of the output voltage value or current value, which is not limited in the present invention.

[0088] Step 102, the PMU measurement unit p...

Embodiment 2

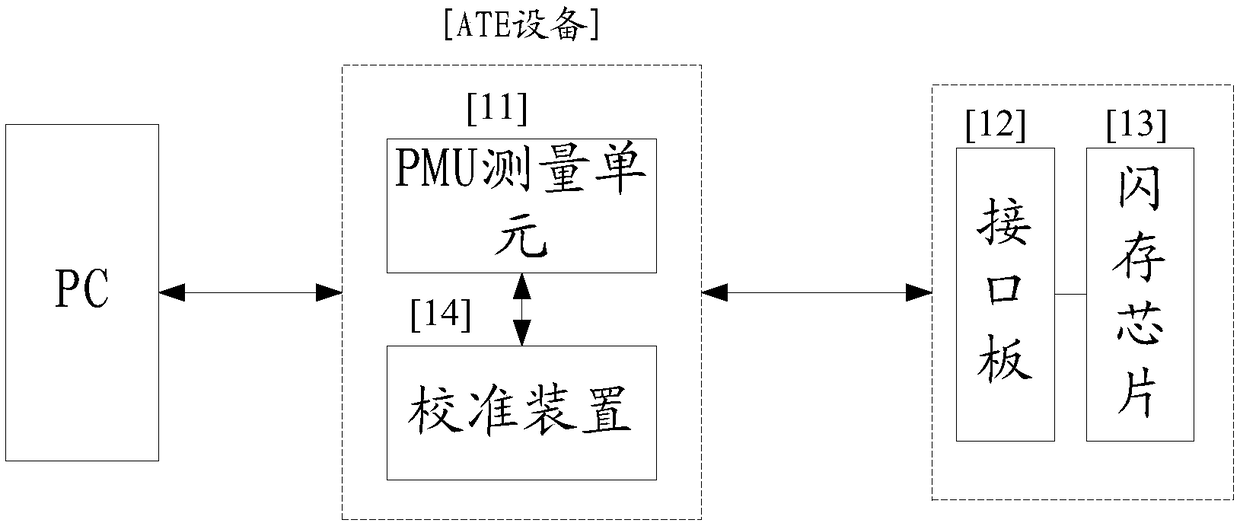

[0109] refer to Figure 5 , The system of the present invention further includes a high-precision measuring instrument; wherein, the high-precision measuring instrument is connected to the interface board of the calibration device, and the high-precision measuring instrument is connected to the PC.

[0110] refer to Figure 6 , which shows a flow chart of a method for calibrating a flash memory chip according to Embodiment 2 of the present invention, which may specifically include the following steps:

[0111] Step 201, the PMU measurement unit receives a second output command sent by the PC; wherein the second output command includes: a second output voltage command or a second output current command.

[0112] Refer to step 101, which will not be described in detail here.

[0113] Step 202, the PMU measurement unit provides a stable second initial power supply to the calibration device interface board according to the second output instruction; wherein, the second initial p...

Embodiment 3

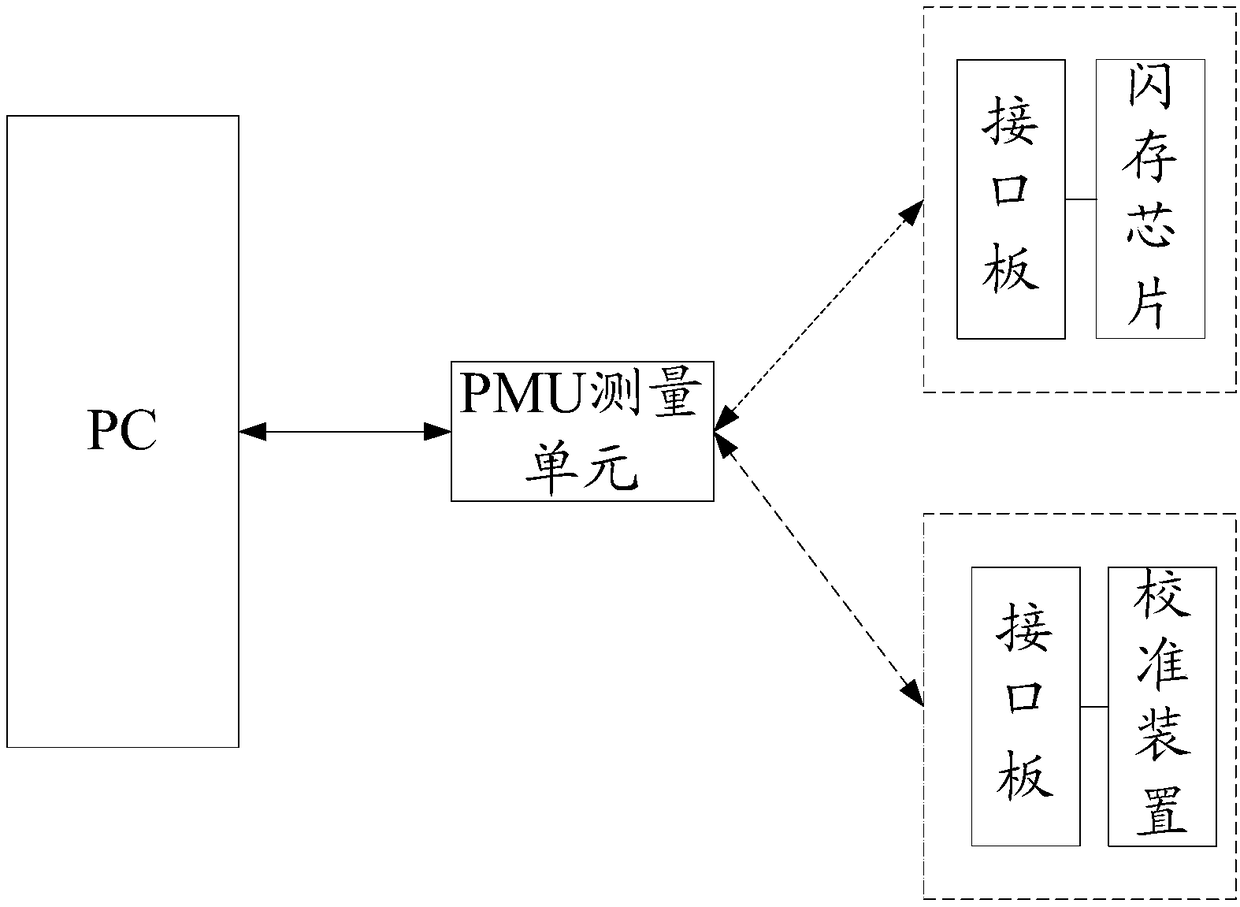

[0128] refer to Figure 7 , shows a structural block diagram of a flash memory chip testing system according to Embodiment 3 of the present invention, the system includes: PC310, PMU measurement unit 320, calibration device interface board 330, flash memory chip interface board 340; wherein, the calibration The device interface board 330 includes: a calibration device 331 and an interface board 332; the calibration device interface board 330 is connected to the PMU measurement unit 320; the PMU measurement unit 320 is connected to the PC310; the flash memory chip interface board 340 and the The interface board 330 of the calibration device is equivalently replaced;

[0129] Described flash memory chip testing system also comprises:

[0130] The first receiving module 321 is used for the PMU measurement unit to receive the first output instruction sent by the PC; wherein, the first output instruction includes: a first output voltage instruction or a first output current instru...

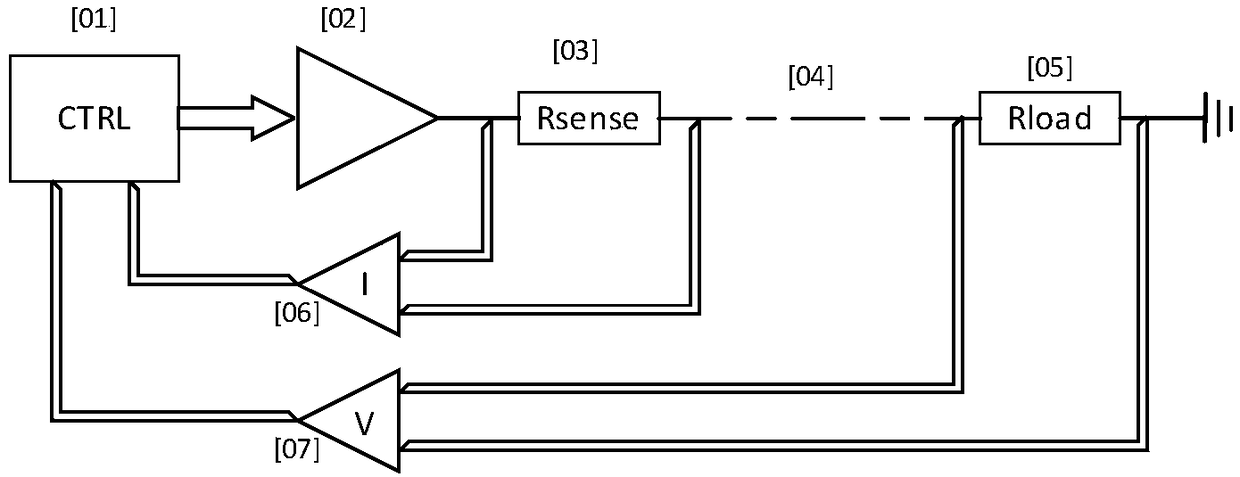

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com