Semiconductor structure and formation method thereof

A technology of semiconductor and hole structure, applied in the field of semiconductor structure and its formation, can solve the problems such as the decrease of product reliability, the influence of the current transmission effect on the surface of the semiconductor layer, and the influence of the product yield rate, etc. The effect of defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Specific implementations of the semiconductor structure and its forming method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

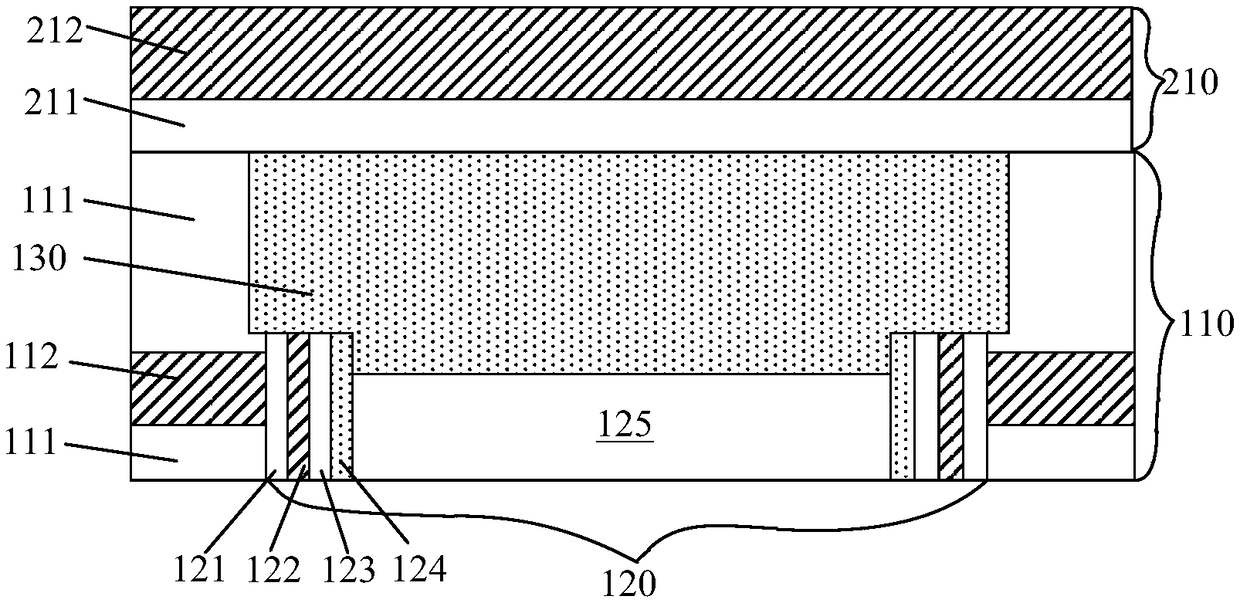

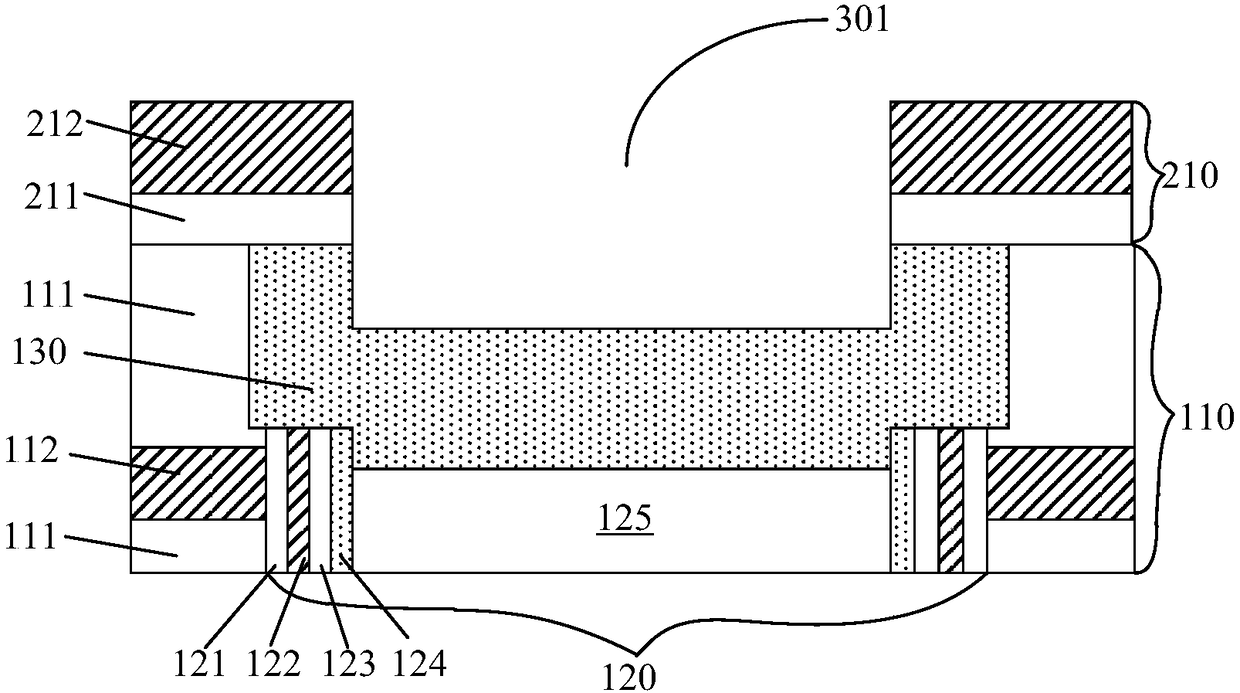

[0026] Please refer to Figure 1 to Figure 8 , is a structural schematic diagram of the formation process of the semiconductor structure according to a specific embodiment of the present invention.

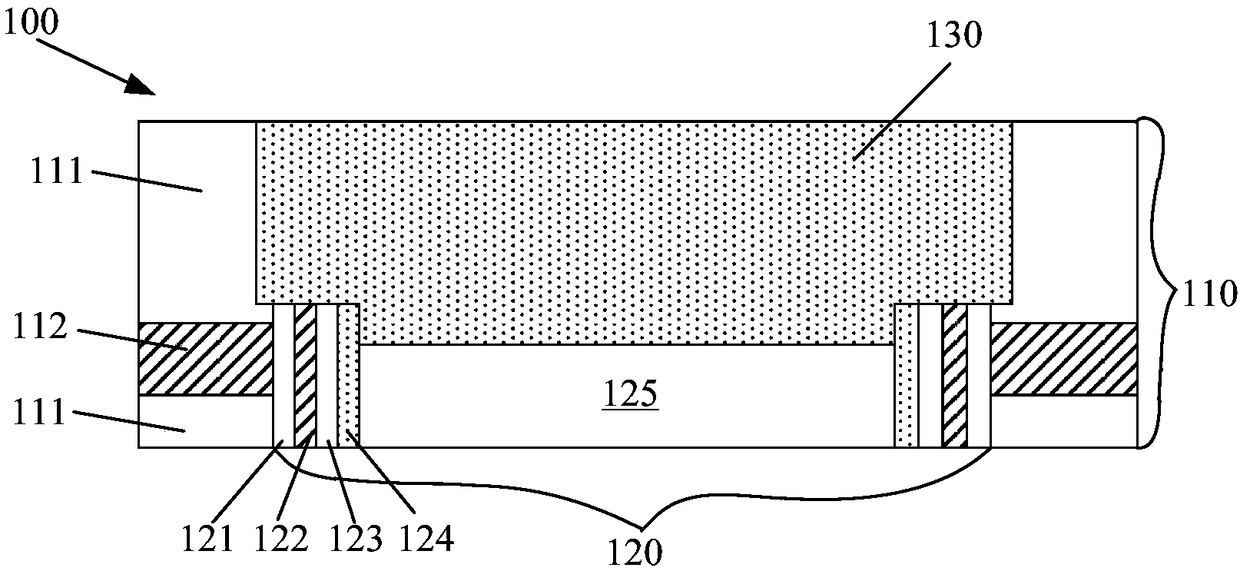

[0027] Please refer to figure 1 A substrate 100 is provided, the substrate 100 includes a first stack structure 110 , a first channel hole structure 120 penetrating through the first stack structure 110 , and a semiconductor layer 130 is formed on the top of the first channel hole structure 120 .

[0028] The base 100 includes a substrate (not shown in the figure), forming a first stacked structure 110 stacked with the surface of the substrate along a direction perpendicular to the surface of the substrate, and the first stacked structure 110 includes first insulating layer 111 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com