Low-noise and high-ground-up-noise-resistant output driving circuit and method

A technology for outputting drive circuits and ground bounce noise, which is applied in logic circuits, logic circuit coupling/interface using field effect transistors, logic circuit connection/interface layout, etc. Ground bounce noise, large static power consumption, etc., to achieve the effect of reducing ground bounce noise, improving the ability to resist high ground bounce noise, and reducing the current rate of change

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

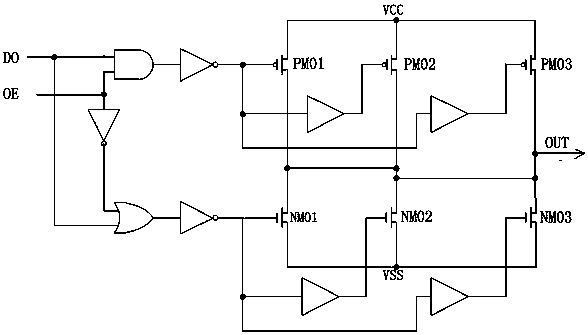

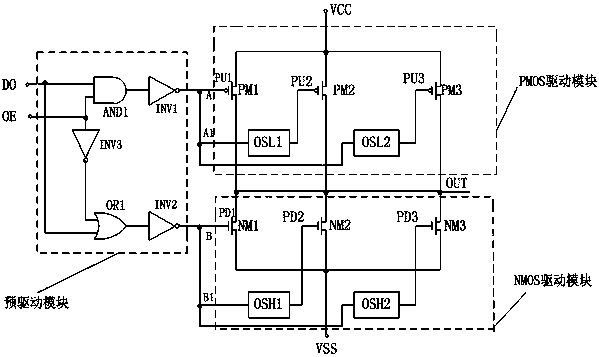

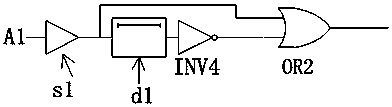

[0043] As an embodiment of the present invention, the PMOS drive module includes a preset number of falling edge delay control sub-modules and PMOS tubes divided into preset groups, and the settings of the preset number of groups and each group The setting of the number of PMOS transistors all meets the actual drive capability of the chip IO, wherein the preset number is equal to the preset number of groups minus one; each group of PMOS transistors in the remaining groups except the first group of PMOS transistors The PMOS transistor corresponds to a falling edge delay control sub-module; in the embodiment of the present invention, in order to simplify the description, the preset number of groups is set to 3, the preset number is set to 2, and all the PMOS transistors in each group are connected in parallel. can be simplified to an equivalent PMOS transistor, such as figure 2 As shown, the first group of PMOS transistors is simplified as the first PMOS transistor PM1, the sec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com