Test Method for Microprocessor Single Event Flip Cross Section

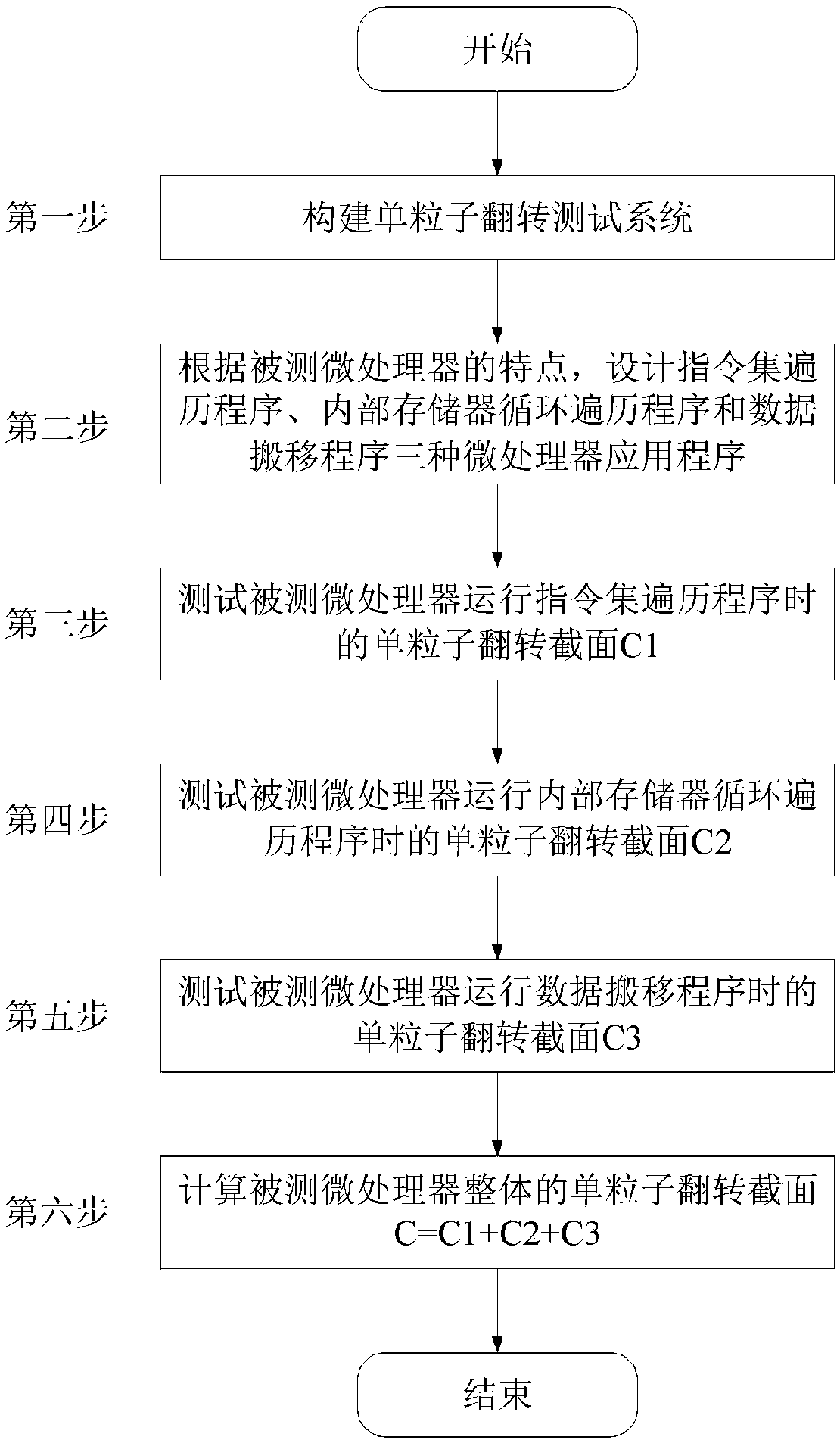

A single-event flipping, microprocessor technology, applied in fault hardware testing methods, electrical digital data processing, instruments, etc., can solve the problem that the single-event flipping cross-section test method of microprocessors cannot comprehensively and accurately reflect the sensitivity of the microprocessor. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

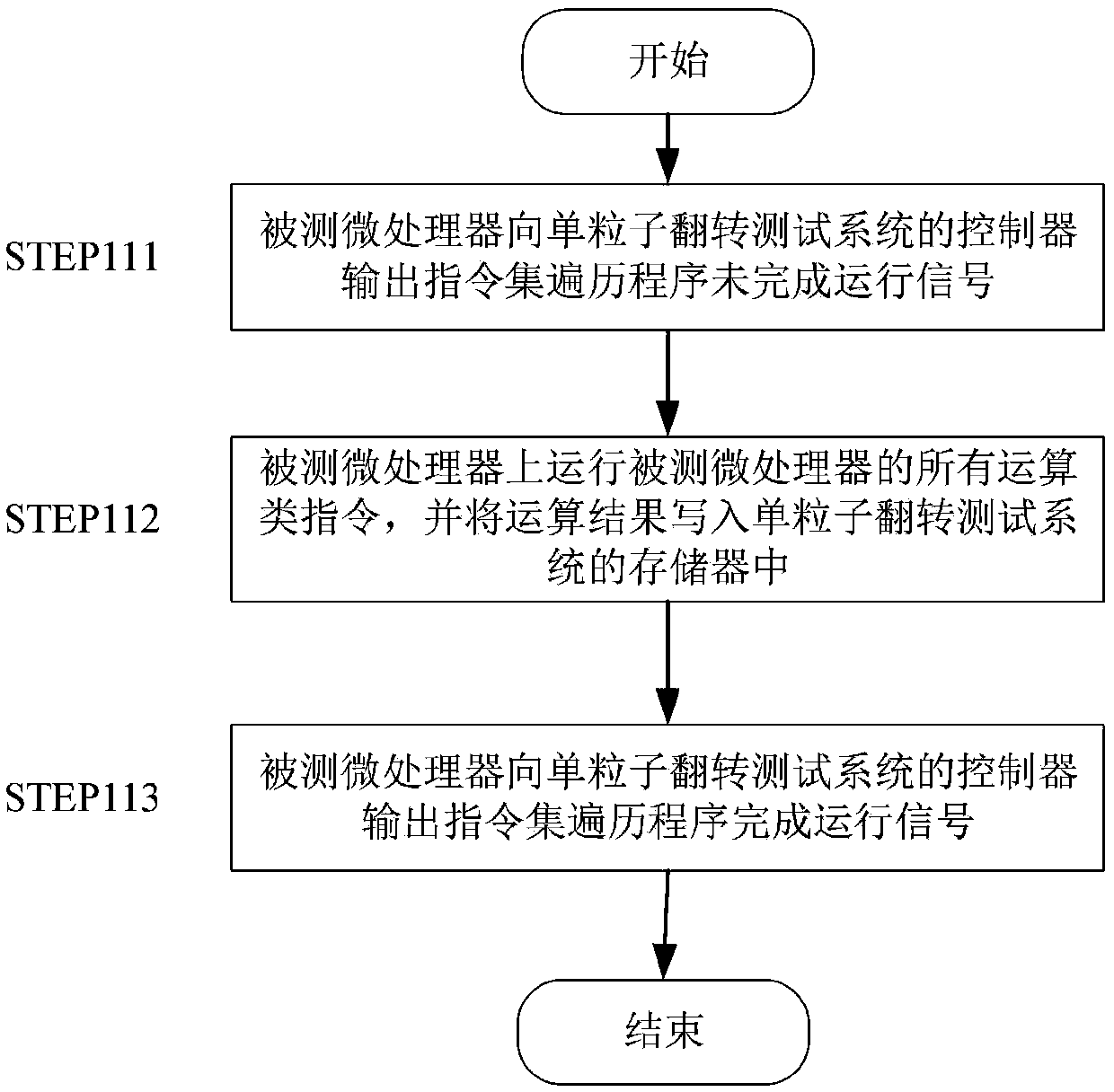

Method used

Image

Examples

Embodiment Construction

[0060] In order to make the purpose and technical solution of the present invention clearer, the present invention will be further described in detail below in conjunction with specific examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0061] In this embodiment, according to the method for testing the single-event inversion cross-section of a microprocessor proposed in the present invention, a single-event inversion cross-section test is performed on a certain type of microprocessor. The microprocessor includes a core, an internal memory, and three peripheral components of an external memory bus interface EMIF, a direct storage access controller DMA, and a multi-channel buffer serial port McBSP.

[0062] The specific implementation steps are as follows:

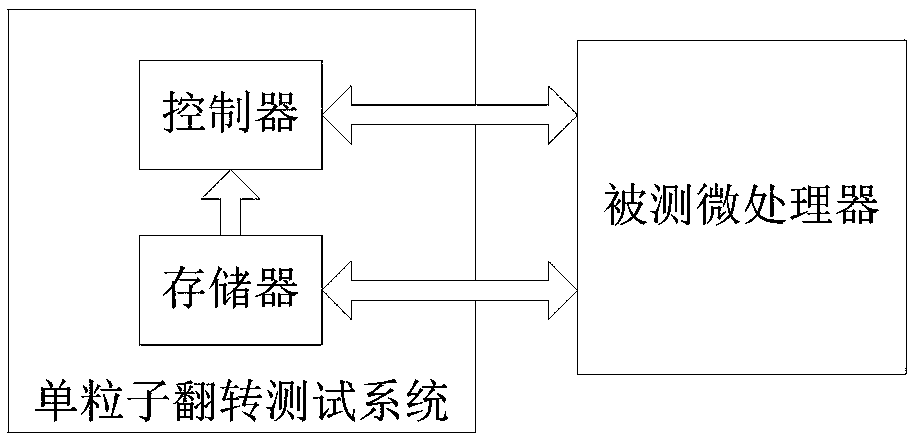

[0063] The first step is to build a single event flip test system. The single event upset test system consis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com