FPGA-based network function acceleration method and system

A technology for network functions and acceleration systems, applied in the field of data processing, can solve the problems of high CPU core occupancy, low resource utilization, low throughput, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] This embodiment discloses an FPGA-based network function acceleration method and system. In the case of no conflict or contradiction, preferred implementation manners of other embodiments may serve as supplements to this embodiment.

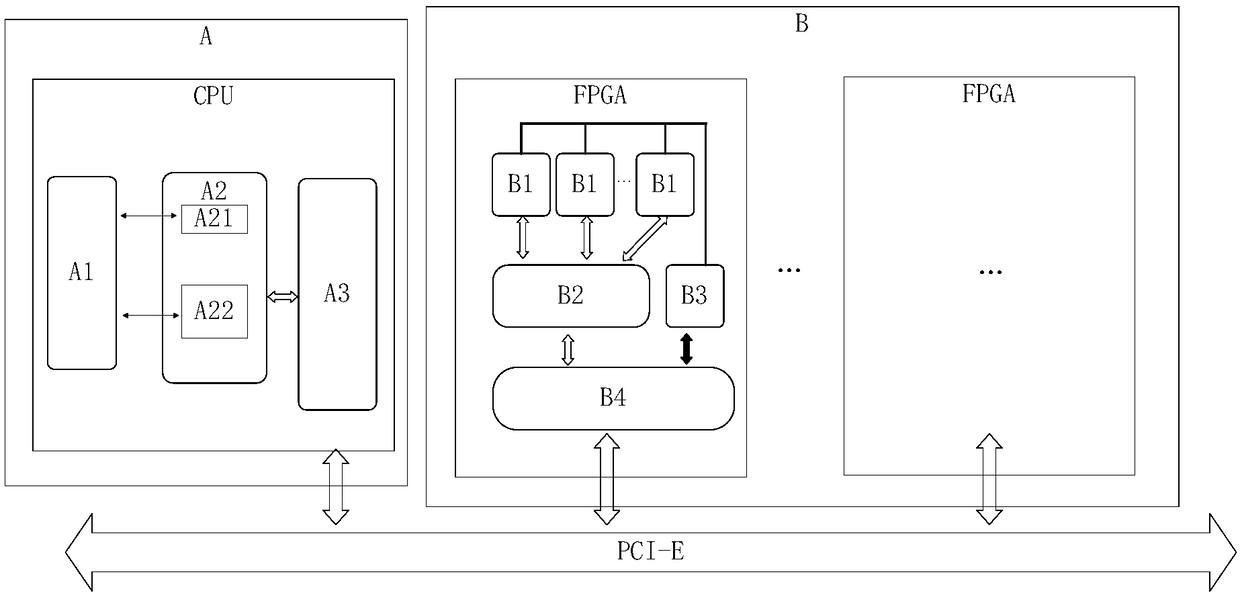

[0042] The present invention provides a network function acceleration method based on FPGA, the method comprising: constructing a network function acceleration system, the system includes a physical machine A and an accelerator card B, the physical machine A and the accelerator card B are connected through a PCIe channel, and the physical machine A Including a processor, the accelerator card B includes an FPGA, and the accelerator card B is used to provide network function acceleration for the processor; the processor is configured to: when the accelerator card is required to provide network function acceleration, query whether the required acceleration already exists in the FPGA module, if yes, obtain the acceleration function ID correspo...

Embodiment 2

[0054] This embodiment is a further improvement on Embodiment 1, and repeated content will not be repeated here. In the case of no conflict or contradiction, preferred implementation manners of other embodiments may serve as supplements to this embodiment.

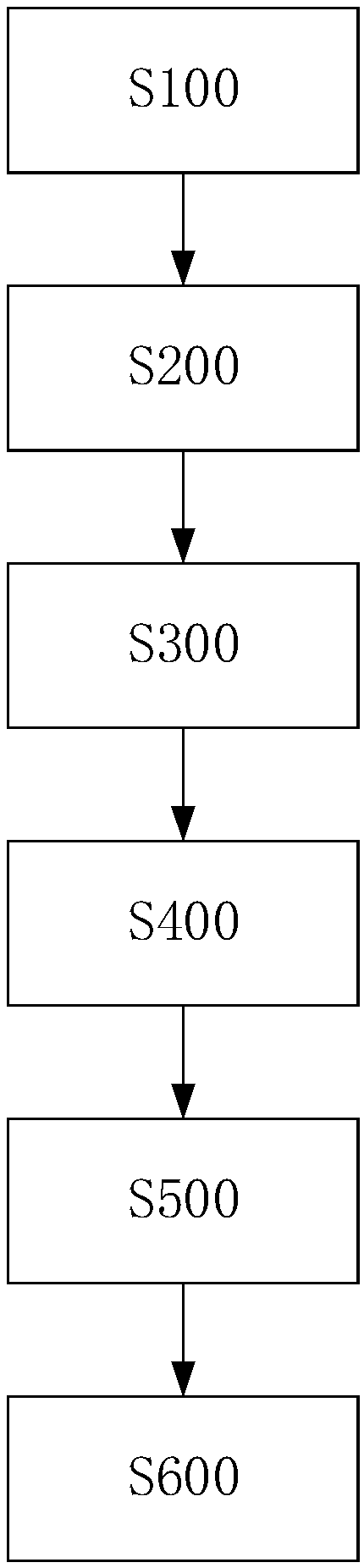

[0055] According to a preferred embodiment, referring to Fig. 2, the method of the present invention may include: step S100, constructing a network function acceleration system, the system may include a physical machine A and an acceleration card B, and the physical machine A and the acceleration card B are connected through a PCIe channel , the accelerator card B includes FPGA. Preferably, the physical machine A may be provided with an acceleration function management module A3. Preferably, the acceleration function management module A3 may be a virtual machine running on the physical machine A. Alternatively, the acceleration function management module A3 may be independent hardware connected to the physical machine A ...

Embodiment 3

[0081] This embodiment is a further improvement on Embodiments 1 and 2 or their combination, and repeated content will not be repeated here. In the case of no conflict or contradiction, preferred implementation manners of other embodiments may serve as supplements to this embodiment.

[0082] According to a preferred embodiment, the method of the present invention may further include: the acceleration function management module A3 associates the required acceleration module with the corresponding network function module A2.

[0083] According to a preferred embodiment, the network function module A2 is a software program that runs on the physical machine A and is independent of each other. For example, a virtual machine. The network function module A2 may include a general processing unit A21 and a computation-intensive unit A22. Preferably, different network function modules A2 have their own independent common processing unit A21 and computation-intensive unit A22. The da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com