Semiconductor device and manufacturing method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their preparation, can solve problems such as uneven thickness, affecting the performance of resistance devices, and poor uniformity of resistance device characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

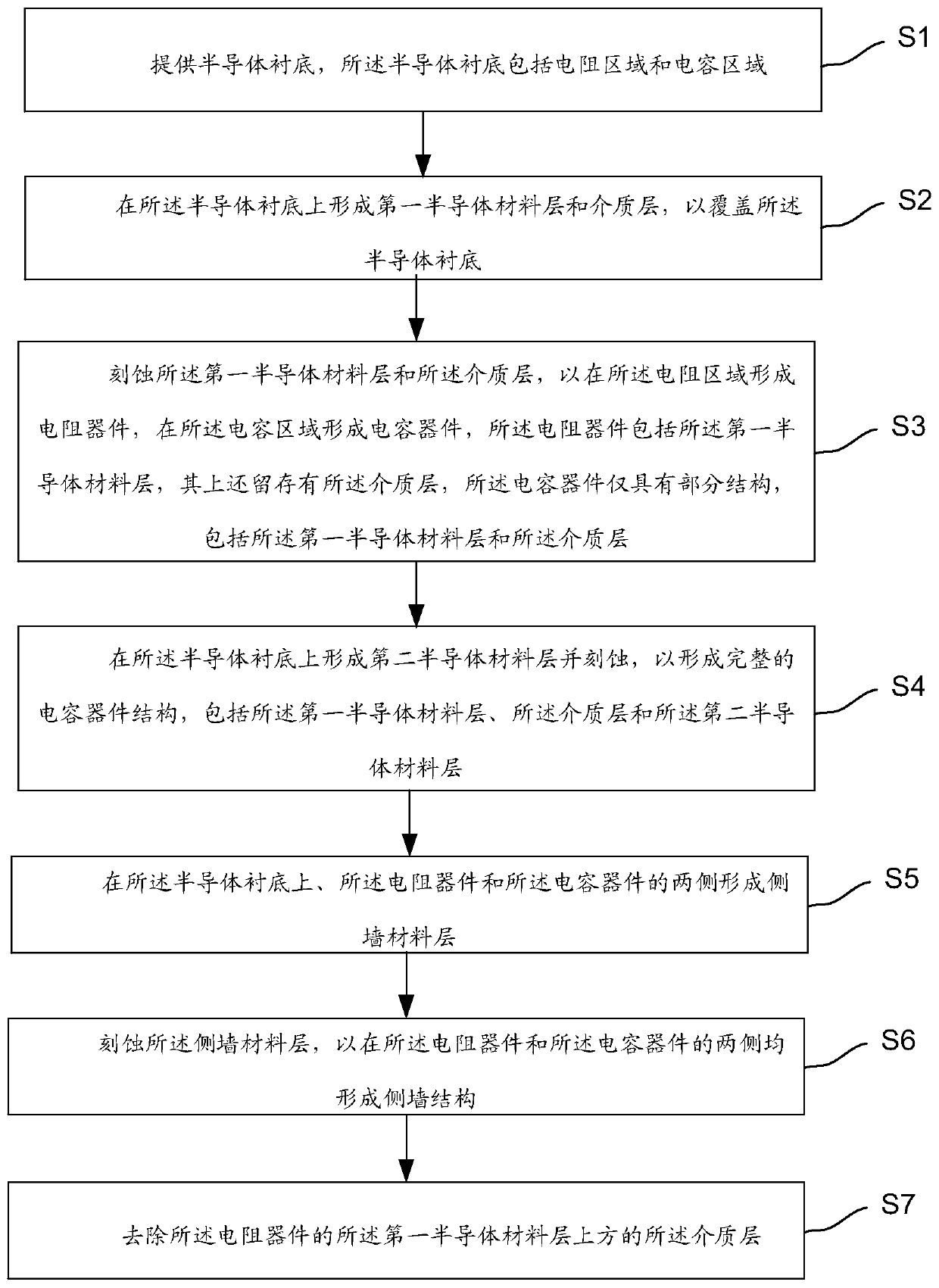

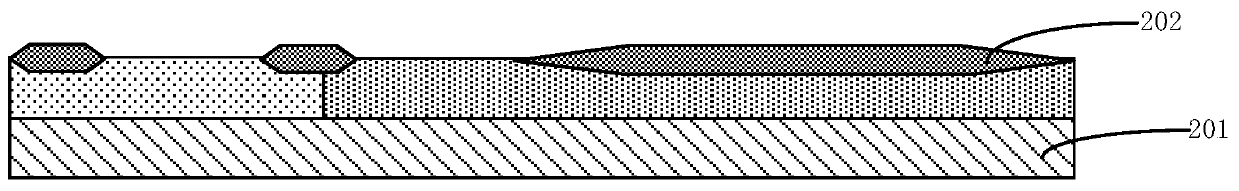

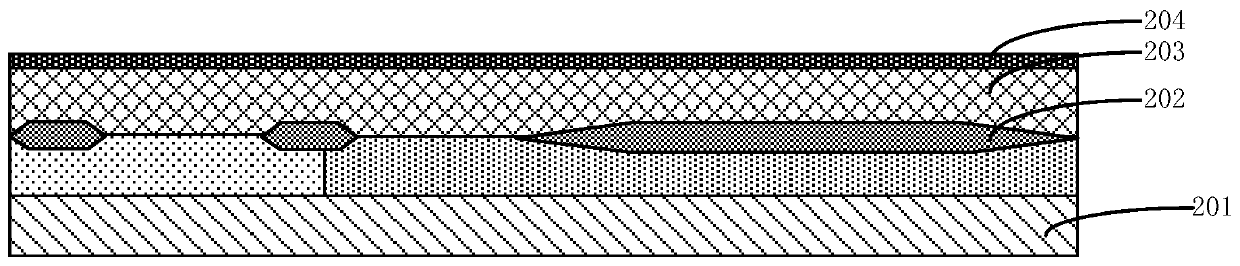

[0043] In order to solve the problems existing in the prior art, the present invention provides a method for preparing a semiconductor device. The structure will be further described below in conjunction with the accompanying drawings, wherein figure 1 Shows a flow chart of the fabrication process of the semiconductor device of the present invention; figure 2A cross-sectional view showing a structure formed in relevant steps of a method for manufacturing a semiconductor device in an embodiment of the present invention; image 3 A cross-sectional view showing a structure formed in relevant steps of a method for manufacturing a semiconductor device in an embodiment of the present invention; Figure 4 A cross-sectional view showing a structure formed in relevant steps of a method for manufacturing a semiconductor device in an embodiment of the present invention; Figure 5 A cross-sectional view showing a structure formed in relevant steps of a method for manufacturing a semicon...

Embodiment 2

[0097] First, step 1 is performed to provide a semiconductor substrate, where the semiconductor substrate includes a resistance region and a capacitance region.

[0098] Specifically, such as figure 2 As shown, a semiconductor substrate 201 is provided, which at least includes a resistive region and a capacitive region.

[0099] Specifically, the semiconductor substrate may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI) , silicon germanium on insulator (SiGeOI) and germanium on insulator (GeOI), etc.

[0100] N-wells and P-wells are formed in the semiconductor substrate, and the methods for forming the N-wells and P-wells can refer to methods commonly used in the art, and are not limited to a certain one, which will not be repeated here.

[0101] Optionally, after forming the N well and the P well, a field oxygen layer 202 is formed on the surface of the semiconduc...

Embodiment 3

[0141] The present invention also provides a semiconductor device, the semiconductor device comprising:

[0142] a semiconductor substrate comprising a resistive region and a capacitive region;

[0143] a resistive device formed in the resistive region, the resistive device comprising the first layer of semiconductor material;

[0144] a capacitive device structure formed in the capacitive region, the capacitive device structure including the first semiconductor material layer, the dielectric layer and the second semiconductor material layer;

[0145] Wherein the dielectric layer above the first semiconductor material layer of the resistance device has been removed.

[0146] Optionally, sidewall structures are formed on sidewalls of the resistive device and the capacitive device structure.

[0147] Wherein, the semiconductor substrate may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com