VLSI (Very Large Scale Integration) design method of fast Fourier transform (FFT)

A technology of Fourier transform and design method, which is applied in computing, special data processing applications, complex mathematical operations, etc., and can solve problems such as low computing speed, large hardware overhead, and large hardware resource overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be described in detail below in conjunction with the accompanying drawings.

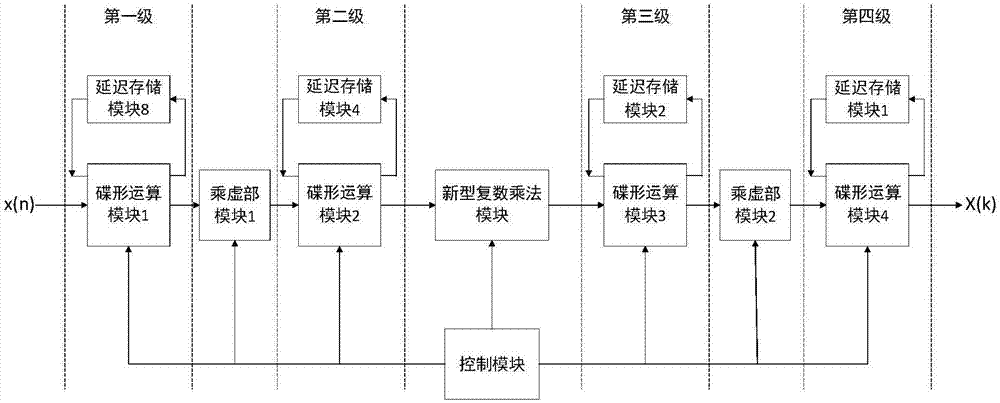

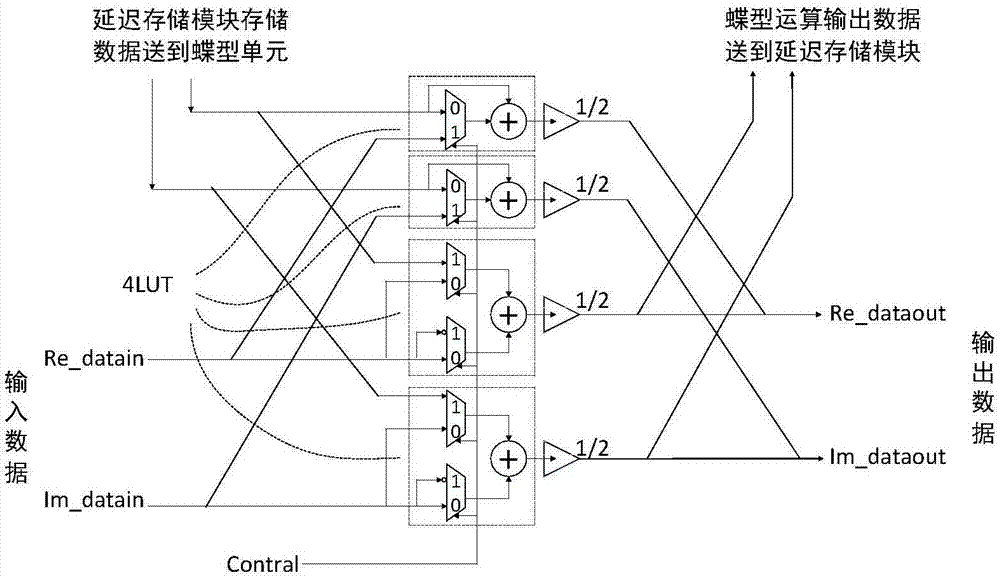

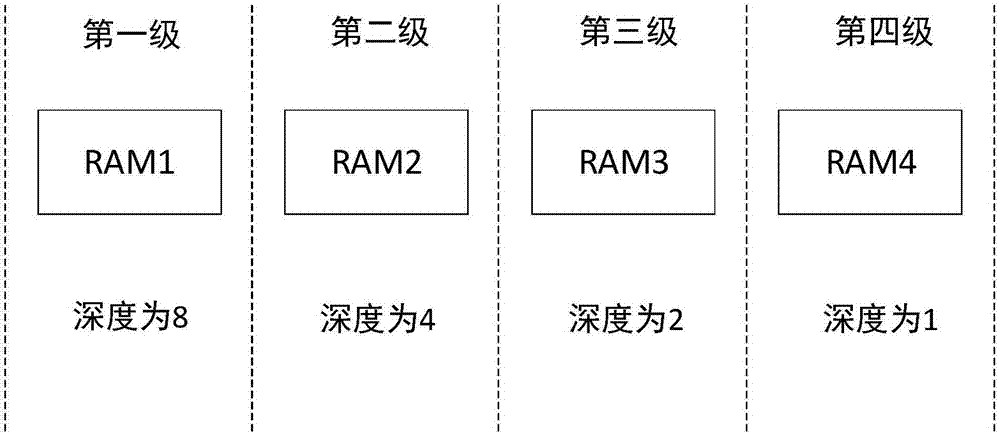

[0021] The present invention is a 16-point high-performance fast Fourier transform architecture, including 4 "selector before adder" butterfly operation modules, 4 delay storage modules, 2 multiplication imaginary part modules, and 1 new complex number Multiplication module and 1 counter control module, the connection mode of several modules is as follows figure 1 shown. It can be seen that the overall structure of FFT is divided into four levels, each level has a "selector before the adder" butterfly operation module and a delay storage module, the two are connected end to end; the new complex multiplication module is in the second level and the third level; the first multiplication imaginary part module is between the first level and the second level, and the second multiplication imaginary part module is between the third level and the fourth level; the function ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com