HEVC-based DVFS control method and system, processor and storage device

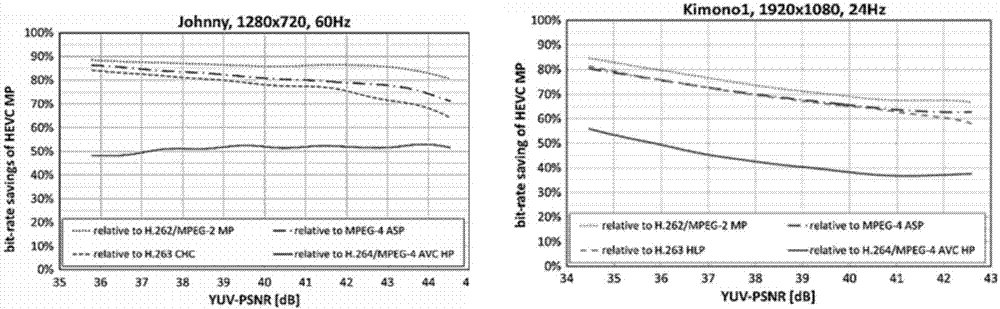

A control method and manager technology, applied in the field of video coding and decoding, can solve the problems of H.265/HEVC decoding workload change, lack of solutions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0095] In order to solve the existing problems introduced in the background technology, the present invention provides an HEVC-based DVFS control method, specifically a CPU-GPU cooperative DVFS energy management control method on an HEVC-based heterogeneous computing platform.

[0096] In order to achieve the above object, the present invention adopts the following technical scheme:

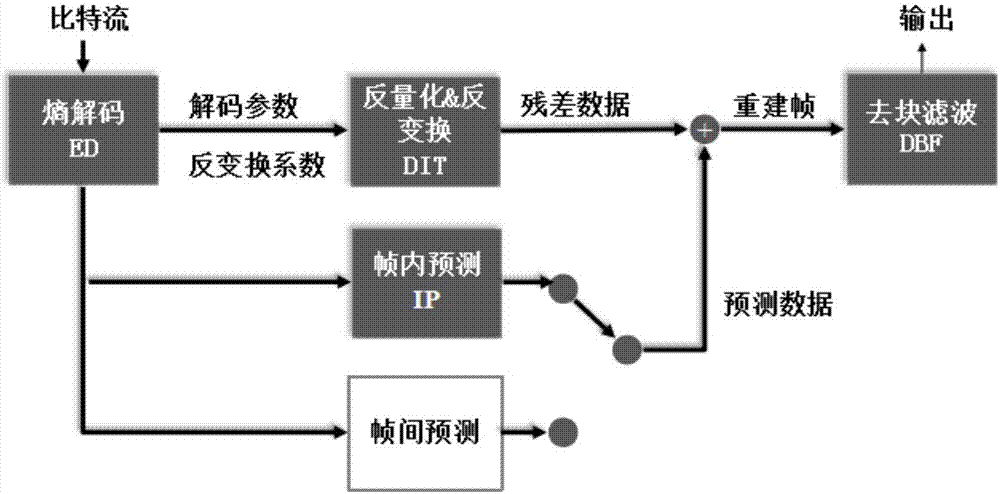

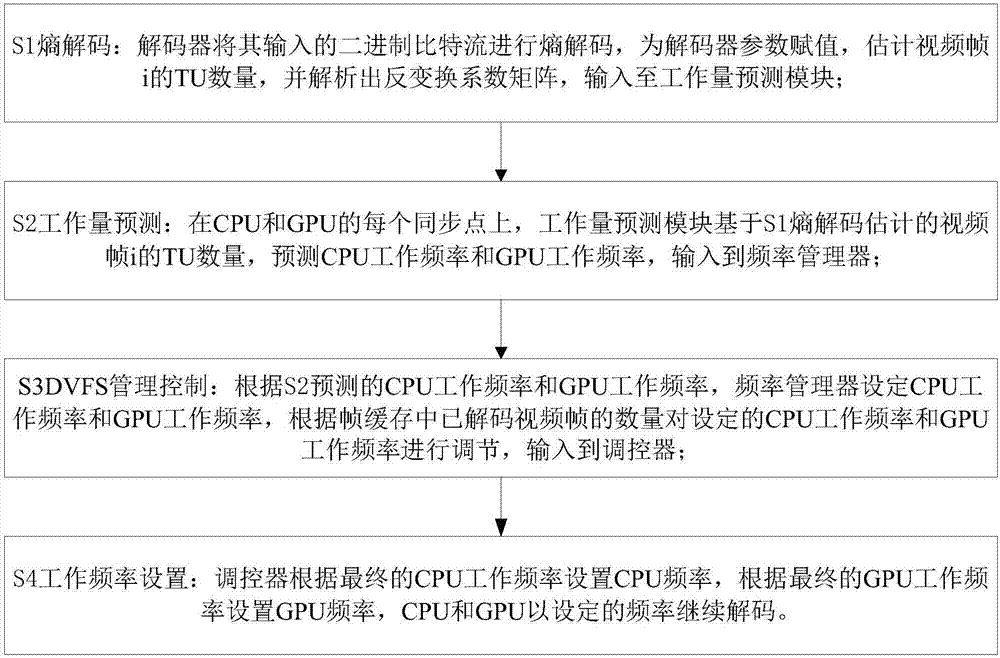

[0097] Such as image 3 as shown,

[0098] A kind of DVFS control method based on HEVC, this method is based on CPU and GPU cooperative HEVC decoding in pipeline mode, and this method comprises the following steps:

[0099] (1) Entropy decoding: the decoder performs entropy decoding on its input binary bit stream, assigns values to the decoder parameters, estimates the number of TUs in the video frame i, and parses out the inverse transformation coefficient matrix, which is input to the workload prediction module;

[0100] (2) Workload prediction: At each synchronization point of the CPU and ...

Embodiment 2

[0166] In order to solve the above-mentioned problems in the background technology, the present invention provides an HEVC-based CPU-GPU cooperative DVFS control system, specifically a CPU-GPU cooperative DVFS energy management control system on an HEVC-based heterogeneous computing platform.

[0167] In order to achieve the above object, the present invention adopts the following technical scheme:

[0168] Such as Figure 13 as shown,

[0169] A HEVC-based CPU-GPU cooperative DVFS control system, the system is based on a HEVC-based DVFS control method, the system includes:

[0170] Decoder, described decoder is used for carrying out entropy decoding to the binary bit stream of its input, assigns a value for decoder parameter, estimates the TU quantity of video frame i, and parses out inverse transform coefficient matrix, input to workload prediction module;

[0171] Workload prediction module, said workload prediction module is used for each synchronization point of CPU and...

Embodiment 3

[0177] In order to solve the above-mentioned problems in the background technology, the present invention provides a processor, specifically a CPU-GPU cooperative heterogeneous computing processor.

[0178] In order to achieve the above object, the present invention adopts the following technical scheme:

[0179] A kind of processor, including CPU and GPU, CPU and GPU coordinate HEVC decoding in a pipelined manner, and call and load and execute each instruction in the storage device:

[0180] (1) Entropy decoding: the decoder performs entropy decoding on its input binary bit stream, assigns values to the decoder parameters, estimates the number of TUs in the video frame i, and parses out the inverse transformation coefficient matrix, which is input to the workload prediction module;

[0181] (2) Workload prediction: At each synchronization point of the CPU and GPU, the workload prediction module predicts the CPU operating frequency and the GPU operating frequency based on th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com