Tristate phase inverter based on FinFET device

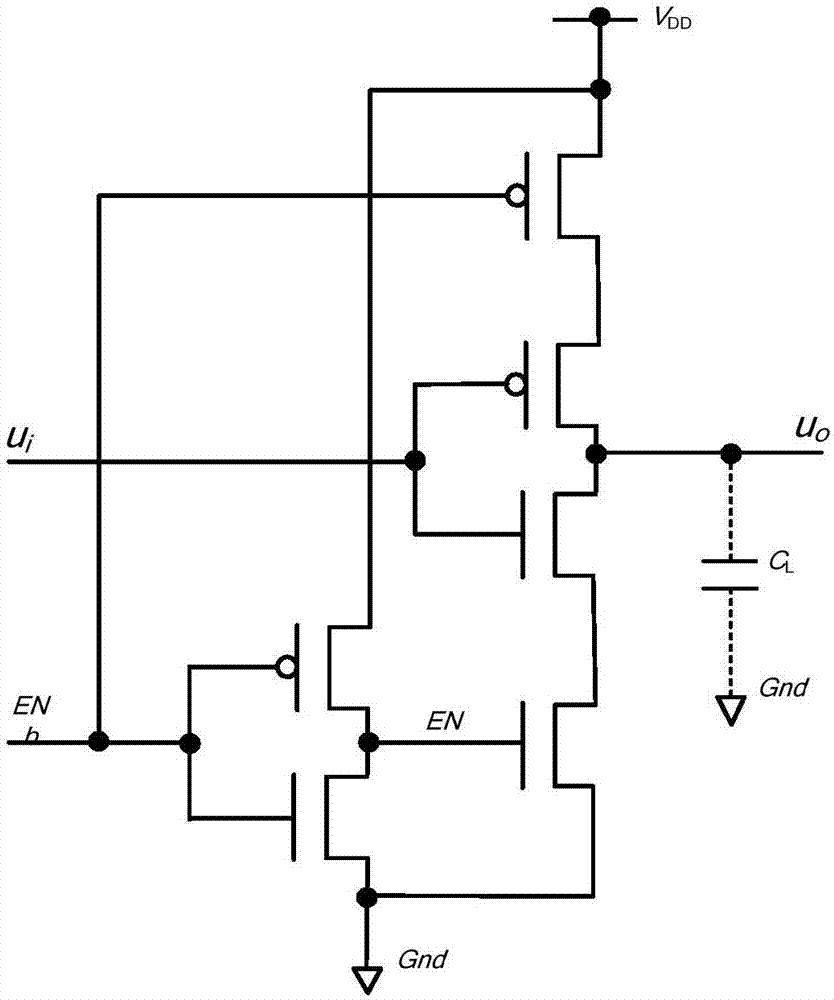

A technology of tri-state inverters and devices, applied to logic circuits with logic functions, etc., can solve problems such as increased leakage current, unimproved tri-state inverter area, and increased leakage power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

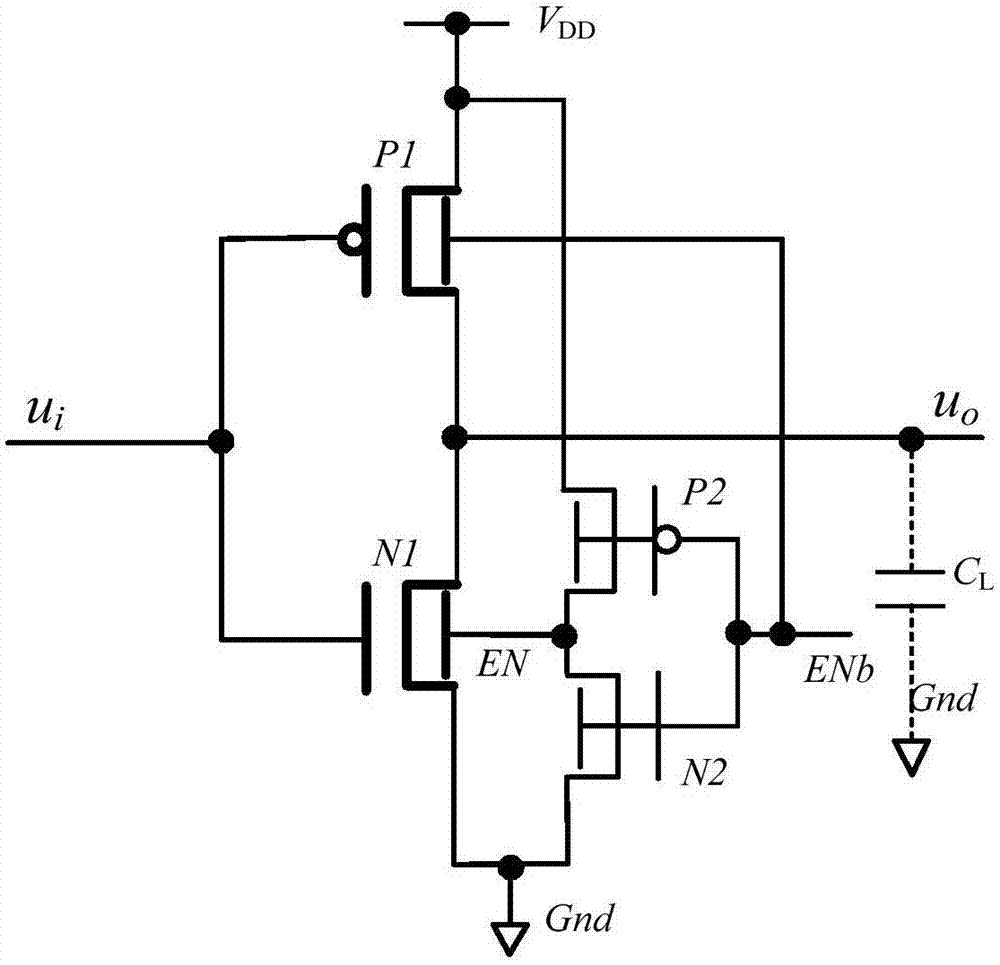

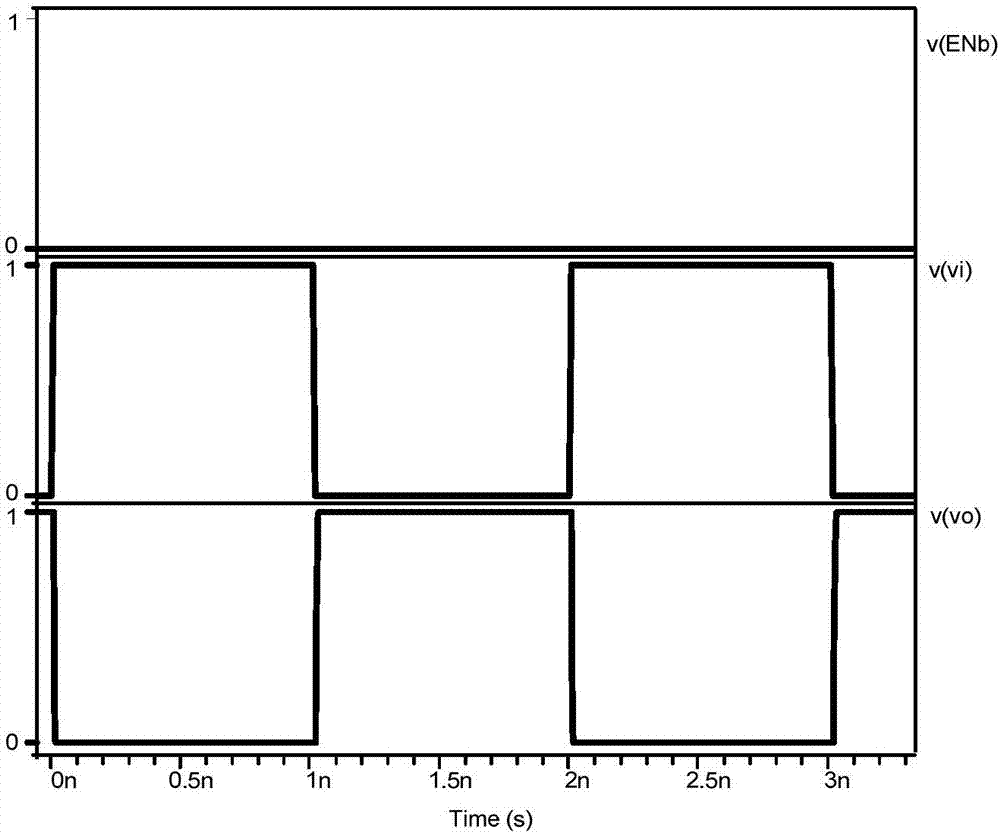

[0015] Embodiment one: if figure 2 As shown, a tri-state inverter based on FinFET devices includes a first N-type FinFET transistor N1, a second N-type FinFET transistor N2, a first P-type FinFET transistor P1, and a second P-type FinFET transistor P2. The P-type FinFET P1 is a high-threshold P-type FinFET, the first N-type FinFET N1 is a high-threshold N-type FinFET, the second P-type FinFET P2 is a low-threshold P-type FinFET, and the second N-type FinFET N2 It is a low-threshold N-type FinFET; the source of the first P-type FinFET P1 and the source of the second P-type FinFET P2 are connected to the power supply VDD, and the front gate of the first P-type FinFET P1 and the first N-type The front gate of the FinFET tube N1 is connected and its connection end is the input terminal of the tri-state inverter, the back gate of the first P-type FinFET tube P1, the front gate of the second P-type FinFET tube P2, and the second P-type FinFET tube P2 The back gate of the second N-...

Embodiment 2

[0016] Embodiment two: if figure 2 As shown, a tri-state inverter based on FinFET devices includes a first N-type FinFET transistor N1, a second N-type FinFET transistor N2, a first P-type FinFET transistor P1, and a second P-type FinFET transistor P2. The P-type FinFET P1 is a high-threshold P-type FinFET, the first N-type FinFET N1 is a high-threshold N-type FinFET, the second P-type FinFET P2 is a low-threshold P-type FinFET, and the second N-type FinFET N2 It is a low-threshold N-type FinFET; the source of the first P-type FinFET P1 and the source of the second P-type FinFET P2 are connected to the power supply VDD, and the front gate of the first P-type FinFET P1 and the first N-type The front gate of the FinFET tube N1 is connected and its connection end is the input terminal of the tri-state inverter, the back gate of the first P-type FinFET tube P1, the front gate of the second P-type FinFET tube P2, and the second P-type FinFET tube P2 The back gate of the second N-...

Embodiment 3

[0018] Embodiment three: as figure 2As shown, a tri-state inverter based on FinFET devices includes a first N-type FinFET transistor N1, a second N-type FinFET transistor N2, a first P-type FinFET transistor P1, and a second P-type FinFET transistor P2. The P-type FinFET P1 is a high-threshold P-type FinFET, the first N-type FinFET N1 is a high-threshold N-type FinFET, the second P-type FinFET P2 is a low-threshold P-type FinFET, and the second N-type FinFET N2 It is a low-threshold N-type FinFET; the source of the first P-type FinFET P1 and the source of the second P-type FinFET P2 are connected to the power supply VDD, and the front gate of the first P-type FinFET P1 and the first N-type The front gate of the FinFET tube N1 is connected and its connection end is the input terminal of the tri-state inverter, the back gate of the first P-type FinFET tube P1, the front gate of the second P-type FinFET tube P2, and the second P-type FinFET tube P2 The back gate of the second N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com