Z-direction interconnection circuit board and manufacturing method thereof

A manufacturing method and circuit board technology, which is applied in multi-layer circuit manufacturing, printed circuit manufacturing, printed circuit, etc., can solve the problems affecting the reliability of sub-board bonding strength, difficulty in filling glue, and easy generation of air bubbles, so as to avoid damage to Insufficient bit space, reducing the difficulty of glue filling, and enhancing the effect of bonding strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods. It should be understood that the specific embodiments described here are only used to explain the present invention, and do not limit the protection scope of the present invention.

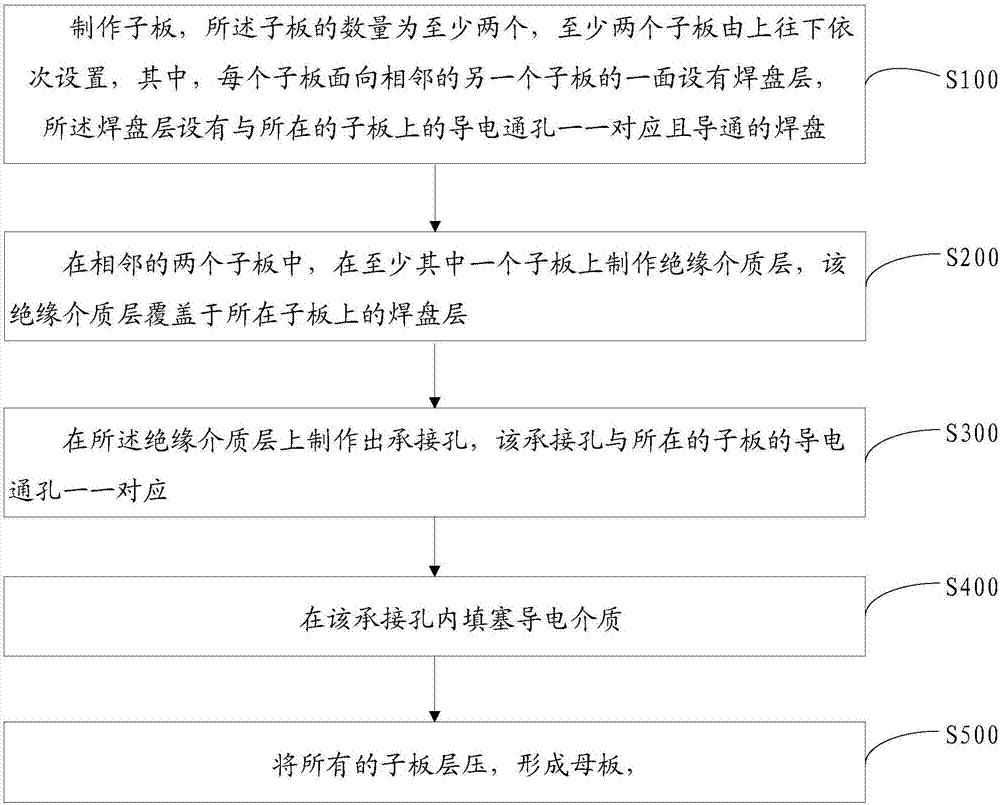

[0031] like figure 1 , Figure 5 , Image 6 and Figure 7 As shown, the manufacturing method of the Z-direction interconnection circuit board of the present invention comprises the following steps:

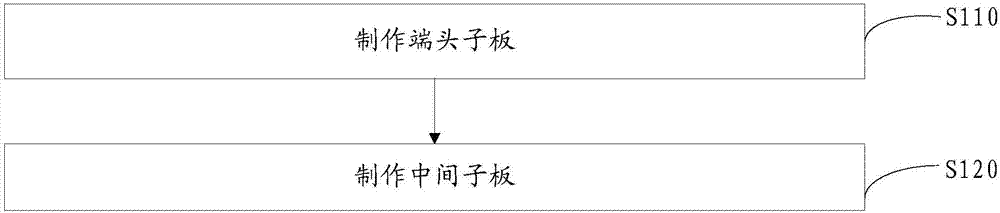

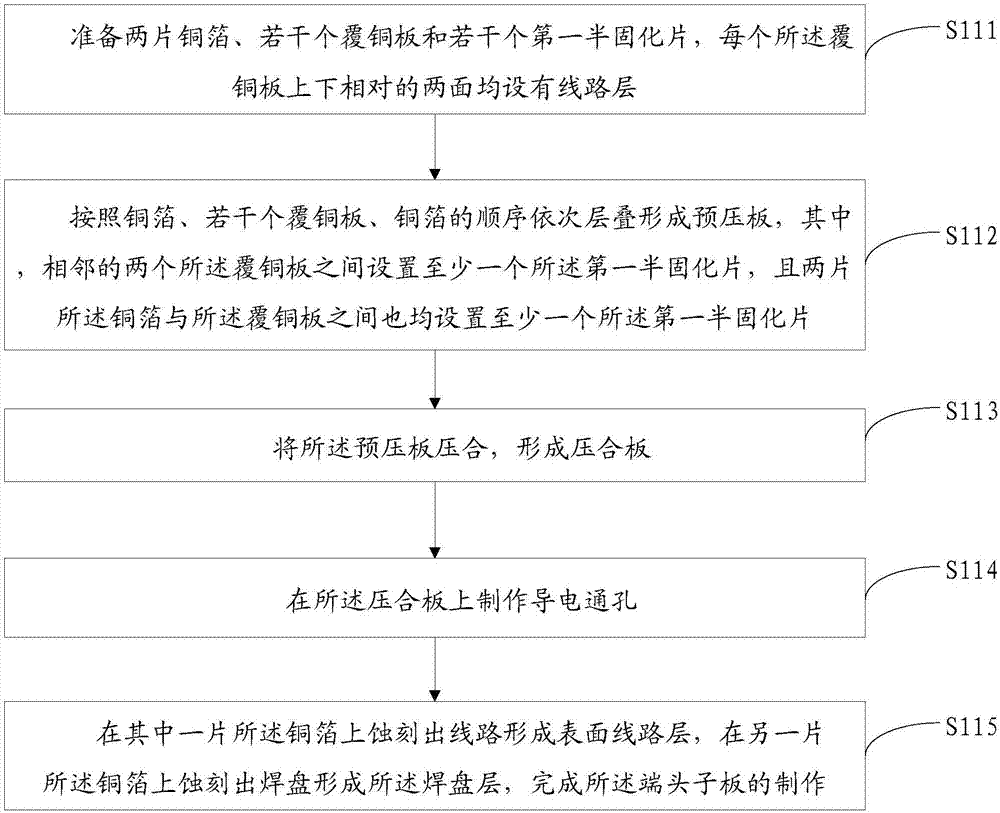

[0032] S100 , making sub-boards 100 , the number of sub-boards 100 is at least two, and the at least two sub-boards 100 are arranged sequentially from top to bottom. Wherein, each sub-board 100 produced is provided with a pad layer (attached to one side facing another adjacent sub-board 100). Figure 5 and Figure 7 padslayer1 , padslayer2 , padslay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com