Physical unclonable function circuit structure based on multiple bunching delay

A functional circuit and grouping technology, which is applied in the field of physical unclonable function circuit structure, can solve the problems of poor uniqueness, insufficient stability, and insufficient performance of physical unclonable functions.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The present invention will be further described below in conjunction with the accompanying drawings.

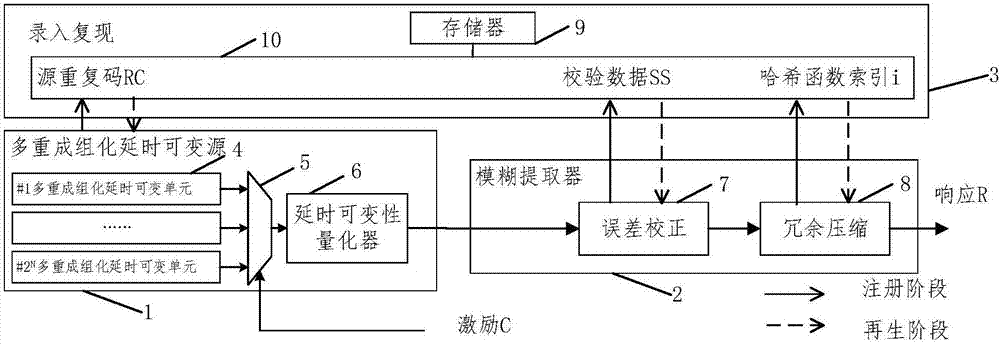

[0013] refer to figure 1 and figure 2 , a physical unclonable function circuit structure based on multiple group delays, using multiple group delay units to realize self-correcting and unique physical unclonable functions, mainly includes the following three parts: multiple grouping Time-delay variable source module (1), fuzzy extractor module (2) and entry recurrence module (3) (see figure 1 ).

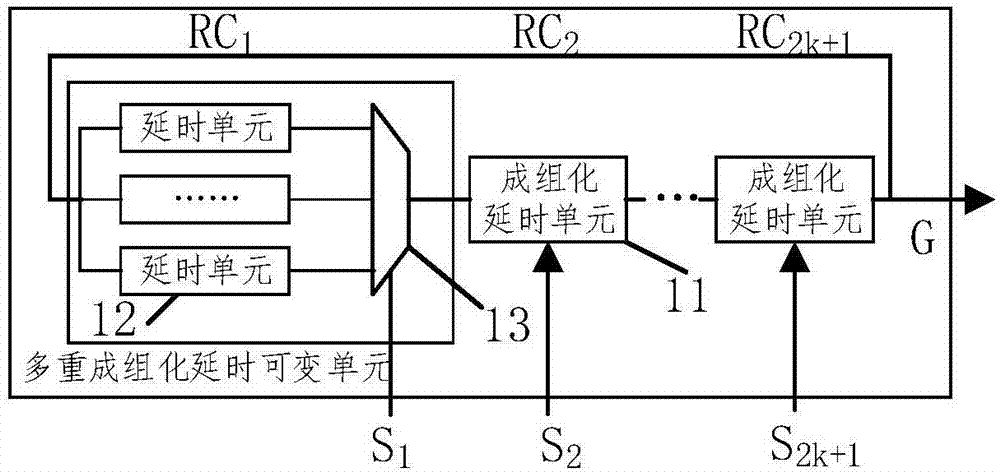

[0014] Multiple Packetized Delay Variable Source Module (1), containing 2 N Multiple grouped delay variable units (4), a 2 N Select 1 selector (5) and a delay variability quantizer (6), obtain the quantization result of the delay variability of the corresponding multiple grouped delay variable unit (4) according to the input excitation signal, obtain source response. Multiple grouping delay variable units (4) comprise 2*k+1 grouping delay units (11), and each grouping ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com