Heterogeneous multi-core processor power consumption control device and method

A multi-core processor and power consumption control technology, applied in the field of multi-core systems, can solve problems such as increasing the difficulty of chip design, complex inter-core communication mechanisms, and increasing additional power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

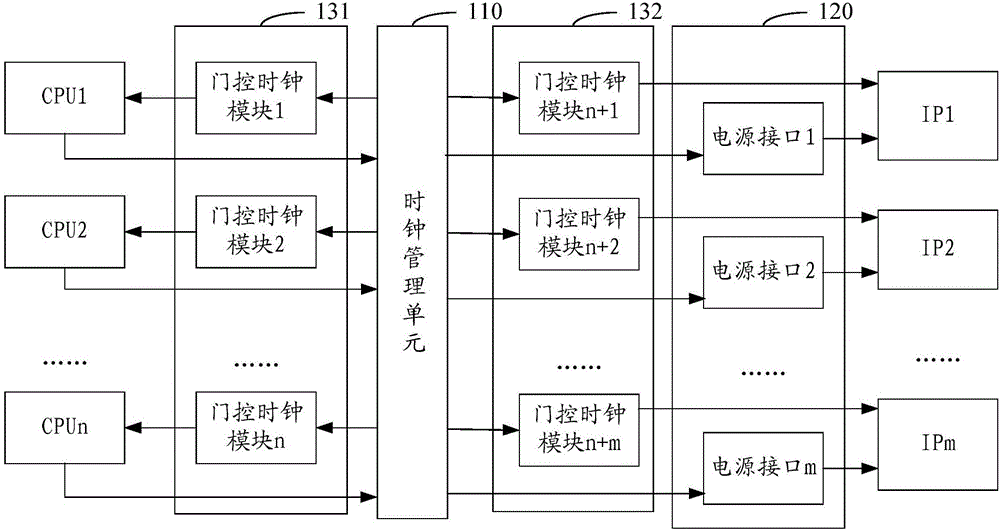

[0021] Embodiment 1 of the present invention provides a device for controlling power consumption of a heterogeneous multi-core processor. see figure 1 As shown, it is a schematic diagram of the composition and structure of the device for controlling power consumption of heterogeneous multi-core processors according to Embodiment 1 of the present invention. Such as figure 1 As shown, the heterogeneous multi-core processor power consumption control device in the first embodiment includes n CPUs (Central Processing Unit, central processing unit) 110 and m IPs (Intellectual Property, intellectual property rights, also called IP cores) 120 , further comprising a clock management unit 110, a power management unit 120 and a clock control unit 130, wherein both n and m are integers greater than 1, and n and m may or may not be equal.

[0022] The power management unit 120 includes m power interfaces, and each power interface is respectively connected to the clock management unit 110...

Embodiment 2

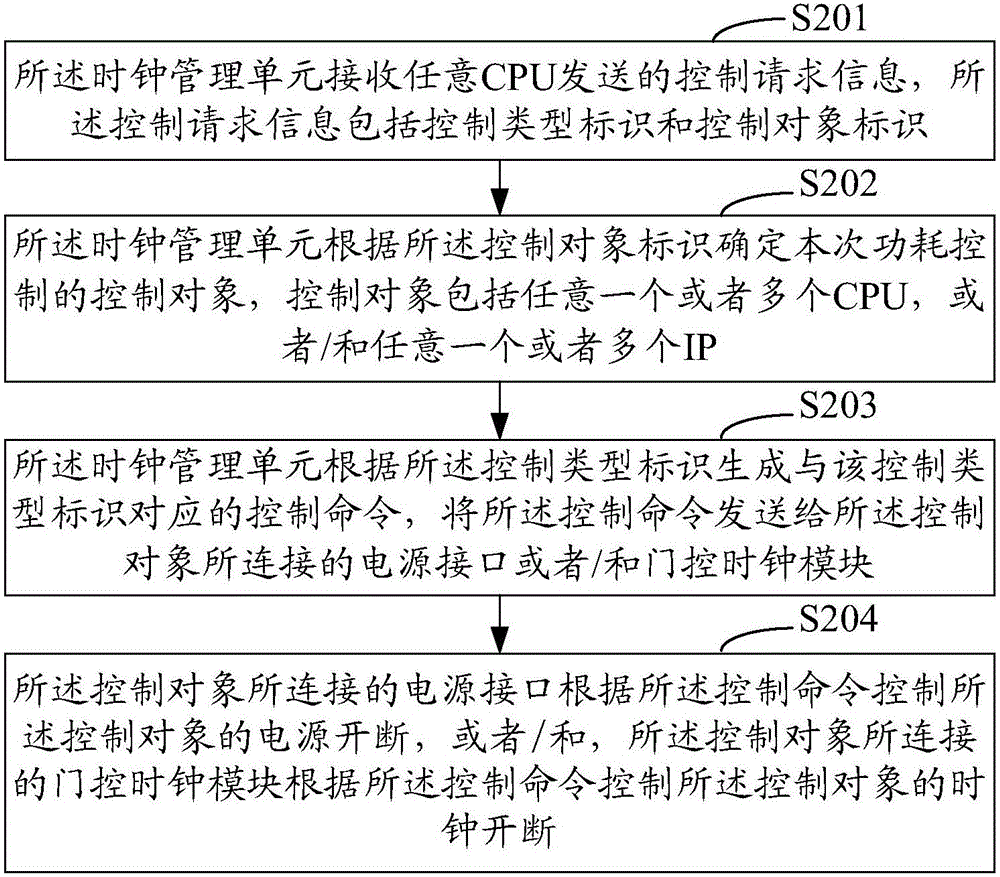

[0047] According to the solution of the device for controlling power consumption of heterogeneous multi-core processors in the first embodiment, embodiment 2 of the present invention provides a method for controlling power consumption of the device for controlling power consumption of heterogeneous multi-core processors. see figure 2 As shown in FIG. 2 , it is a schematic flowchart of the implementation of the power consumption control method of the heterogeneous multi-core processor power consumption control device according to Embodiment 2 of the present invention. Such as figure 2 As shown, the power consumption control method of the heterogeneous multi-core processor power consumption control device in this embodiment includes:

[0048] Step S201: the clock management unit receives control request information sent by any CPU, and the control request information includes a control type identifier and a control object identifier;

[0049] Step S202: The clock management ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com