Thin film transistor and making method thereof

A technology of thin film transistors and manufacturing methods, applied in the field of thin film transistors and their manufacturing, capable of solving problems such as unfavorable development of thin-type displays and increase of overall thickness, and achieving the effect of being conducive to the development of thin-type displays and reducing overall thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

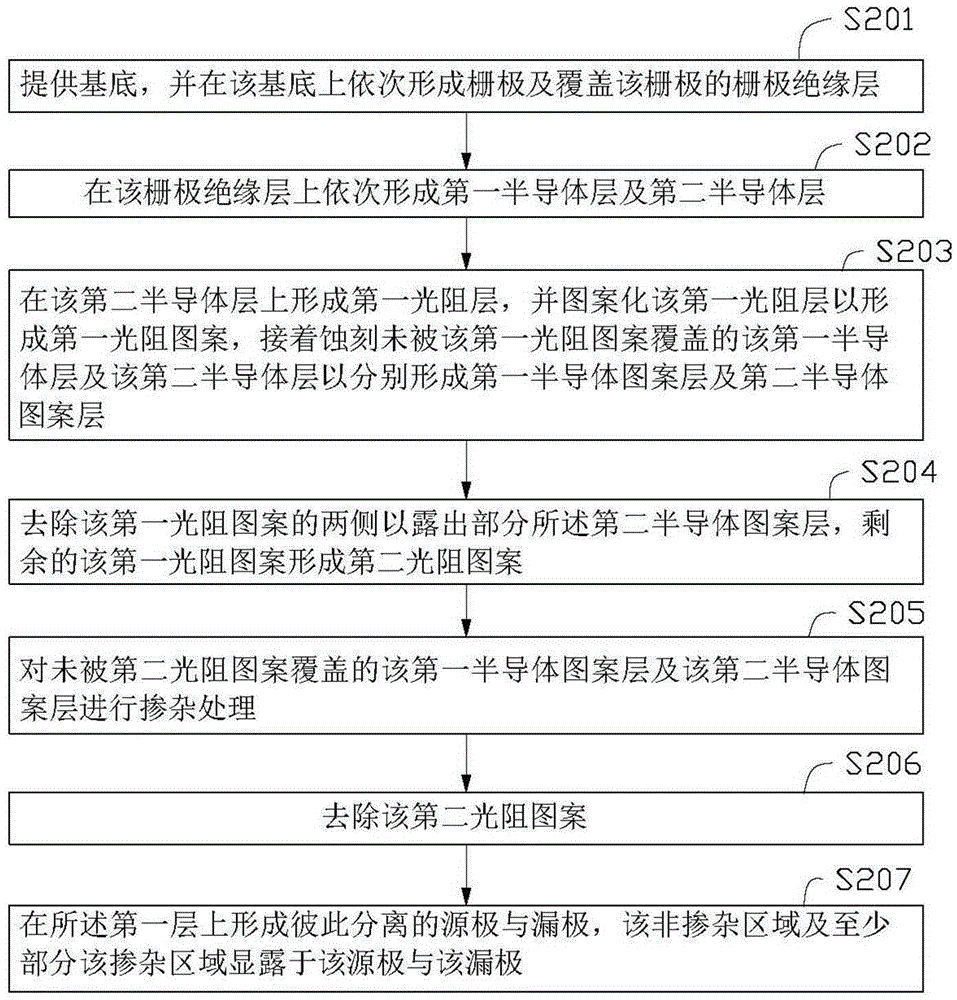

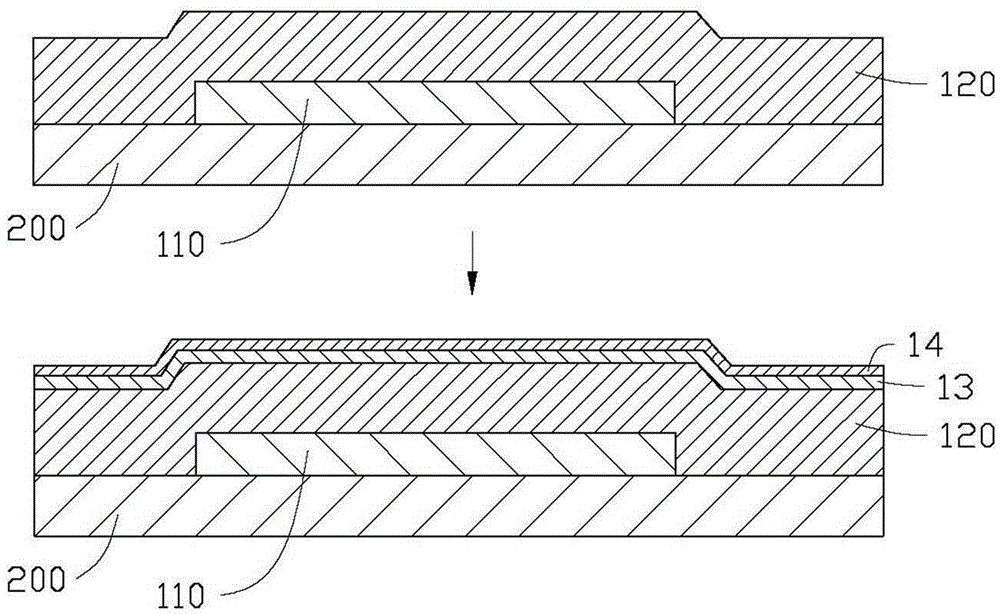

[0019] see figure 1 , a cross-sectional view of the structure of the thin film transistor 100 provided by the present invention. The TFT 100 is formed on a substrate 200 , and the TFT 100 includes a gate 110 , a gate insulating layer 120 , an intrinsic amorphous silicon layer 160 , a source 151 and a drain 152 . The gate 110 is located on the substrate 200, the gate insulating layer 120 covers the substrate 200 and the gate 110, and the intrinsic amorphous silicon layer 160 is disposed on the side of the gate insulating layer 120 away from the substrate 200. and located at a position corresponding to the gate 110 . The gate insulating layer 120 is used to insulate the gate 110 from the intrinsic amorphous silicon layer 160 , the source 151 and the drain 152 . The intrinsic amorphous silicon layer 160 further includes a first layer 131 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com