CIC filter design method based on parallel computation

A filter design, filter technology, applied in impedance networks, digital technology networks, electrical components, etc., can solve problems such as processing speed limitations, and achieve the effect of ensuring system operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

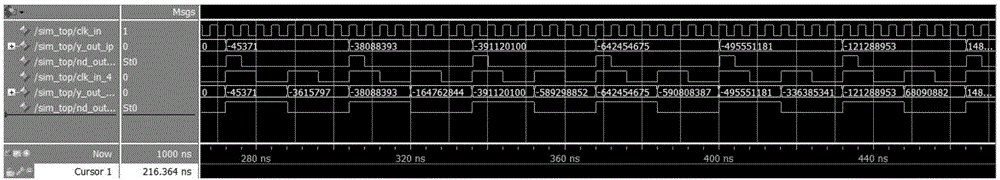

[0068] In Embodiment 1, the operation results of a single-stage parallel CIC filter are compared with those of a traditional single-stage serial CIC filter.

[0069] Let the input signal sampling frequency be f s = 1GHz. The operating frequency of traditional single-stage serial CIC needs to be within f s = 1 GHz. In the parallel CIC design of the present invention, M=4, D=8, and the single-stage CIC filter is equivalent to Q=1. Parallel filters operate at f cic = f s / M=250MHz.

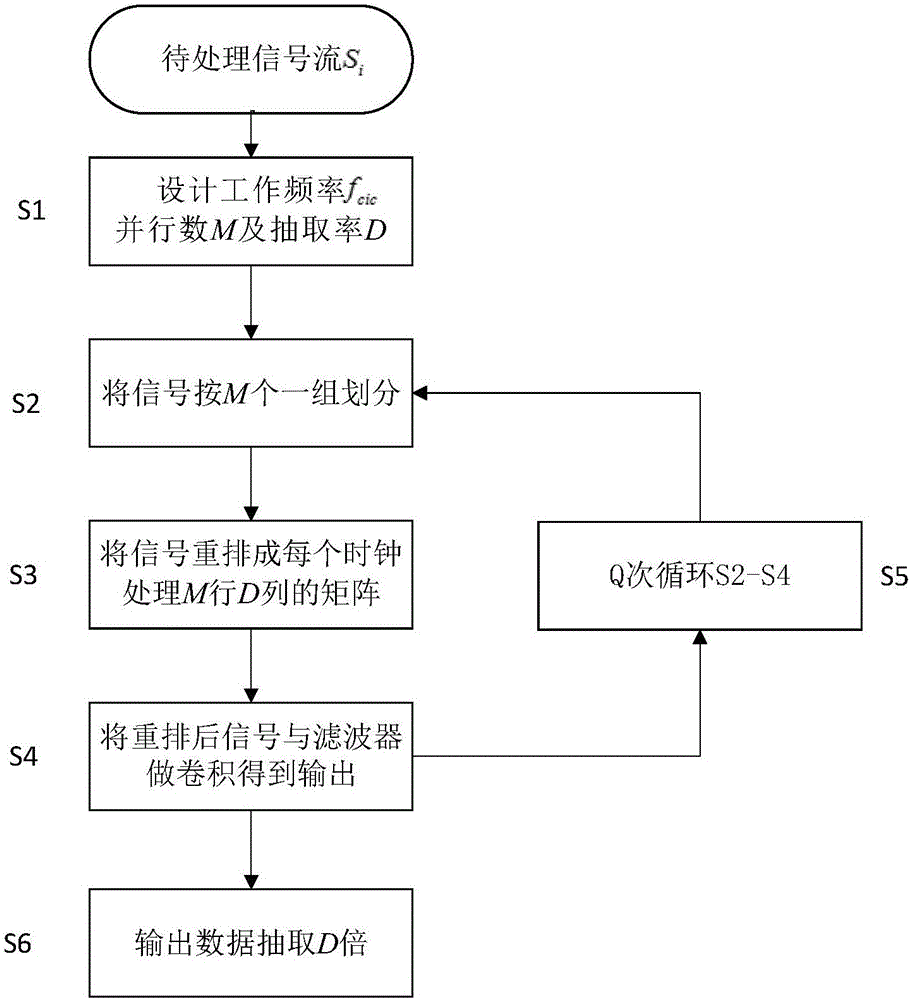

[0070] The single-stage parallel CIC filter design in embodiment 1 comprises the following steps:

[0071] ①For the sampling rate f s = 1GHz input signal S i , 0≤i≤N (where N is a fixed data length). We design the filter to operate at f cic =250MHz, the parallel number is M=4. Determine the sampling number D=8;

[0072] ② Divide it into groups of 4 data, and divide the signal flow S i , 0≤i≤N becomes the following formula:

[0073] {(S 0 ,S 1 ,...,S 3 ),(S 4 ,S 5 ,...,S 7 ),…}

...

Embodiment 2

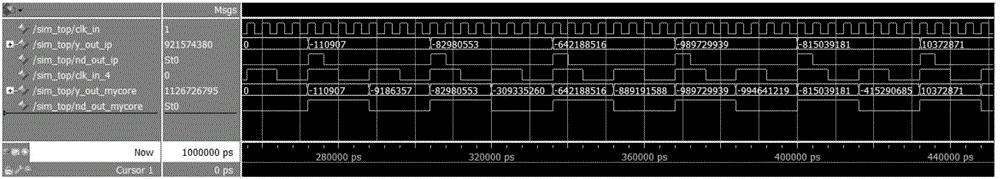

[0085] In Embodiment 2, the operating results of the multi-stage parallel CIC filter are compared with those of the traditional multi-stage serial CIC filter.

[0086] Let the input signal sampling frequency be f s = 1GHz. The operating frequency of traditional single-stage serial CIC needs to be within f s = 1 GHz. In the parallel CIC design of the present invention, M=4, D=8, and the single-stage CIC filter is equivalent to Q=1. Parallel filters operate at f cic = f s / M=250MHz.

[0087] The multistage parallel CIC filter design in embodiment 2 comprises the following steps:

[0088] ①For the sampling rate f s = 1GHz input signal S i , 0≤i≤N (where N is a fixed data length). We design the filter to operate at f cic =250MHz, the parallel number is M=4. Determine the sampling number D=8;

[0089] ② Divide it into groups of 4 data, and divide the signal flow S i , 0≤i≤N becomes the following formula:

[0090] {(S 0 ,S 1 ,...,S 3 ),(S 4 ,S 5 ,...,S 7 ),…}

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com