Unit package body die and precise forming die for chip region exposed package

A chip area and package technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of fit clearance, interference fit, affecting the function of the exposed area of the chip, etc., so as to reduce the processing difficulty and ensure the processing accuracy. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with the drawings and embodiments.

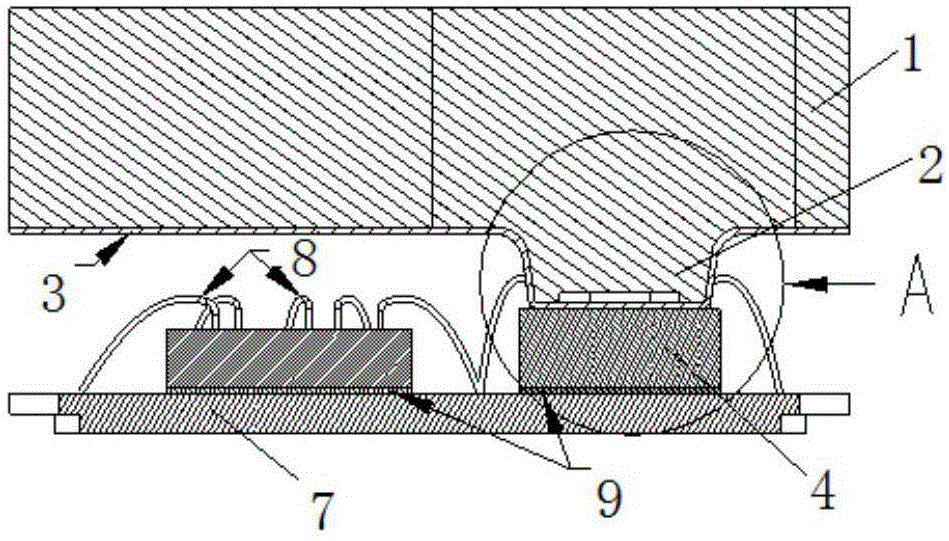

[0032] Such as Figure 5-Figure 6 As shown, a precision molding die for bare packaging of chip area includes multiple unit package molds 1 spliced with each other, multiple unit package molds 1 are arranged in rows, and adjacent unit package molds 1 are spliced Combine into one. The multiple unit package molds 1 are arranged in rows and spliced together to form a whole, which can be matched with multiple bare chips to realize packaging molding containing multiple bare chips.

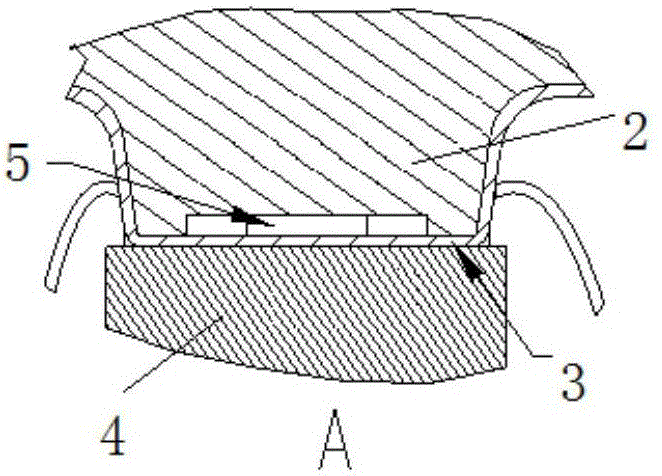

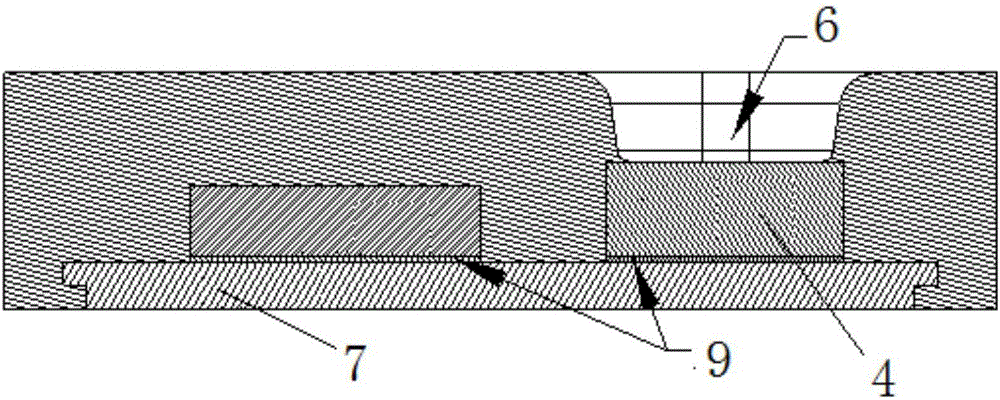

[0033] Such as Figure 1-Figure 4 As shown, the unit package mold 1 includes a fixed support body 10, a movable molding assembly 11 is embedded at a set position in the fixed support body 10, a boss 2 is provided at one end of the molding assembly 11, and the other end of the molding assembly 11 and movable elements It cooperates to realize that the boss 2 protrudes and fixes the support body ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com