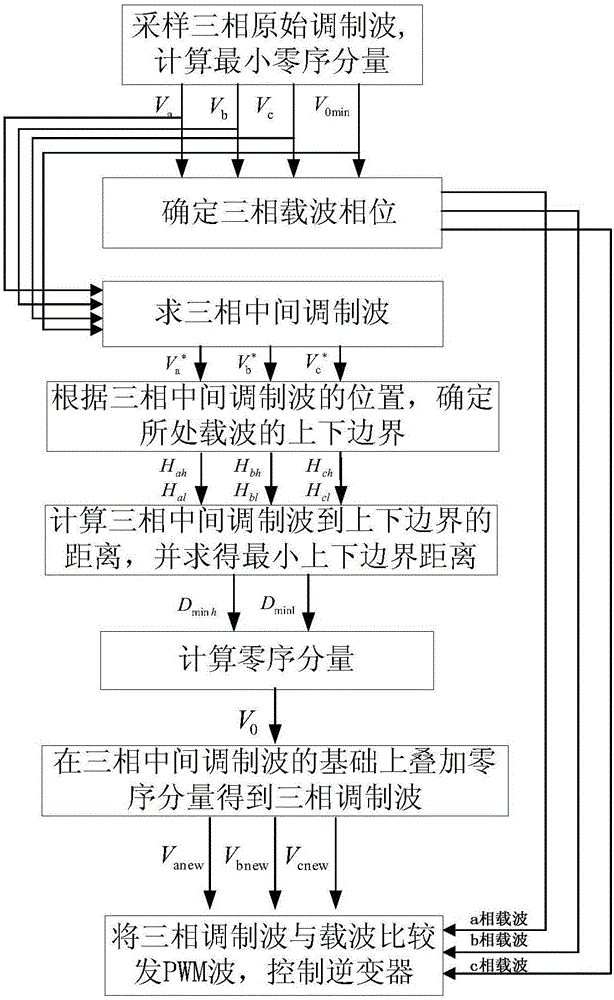

Carrier implementation method for low common-mode voltage modulation of three-phase five-level inverter

A common-mode voltage and inverter technology is applied in the field of carrier realization of a three-phase five-level inverter low common-mode voltage modulation strategy, and can solve problems such as low total harmonic distortion rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

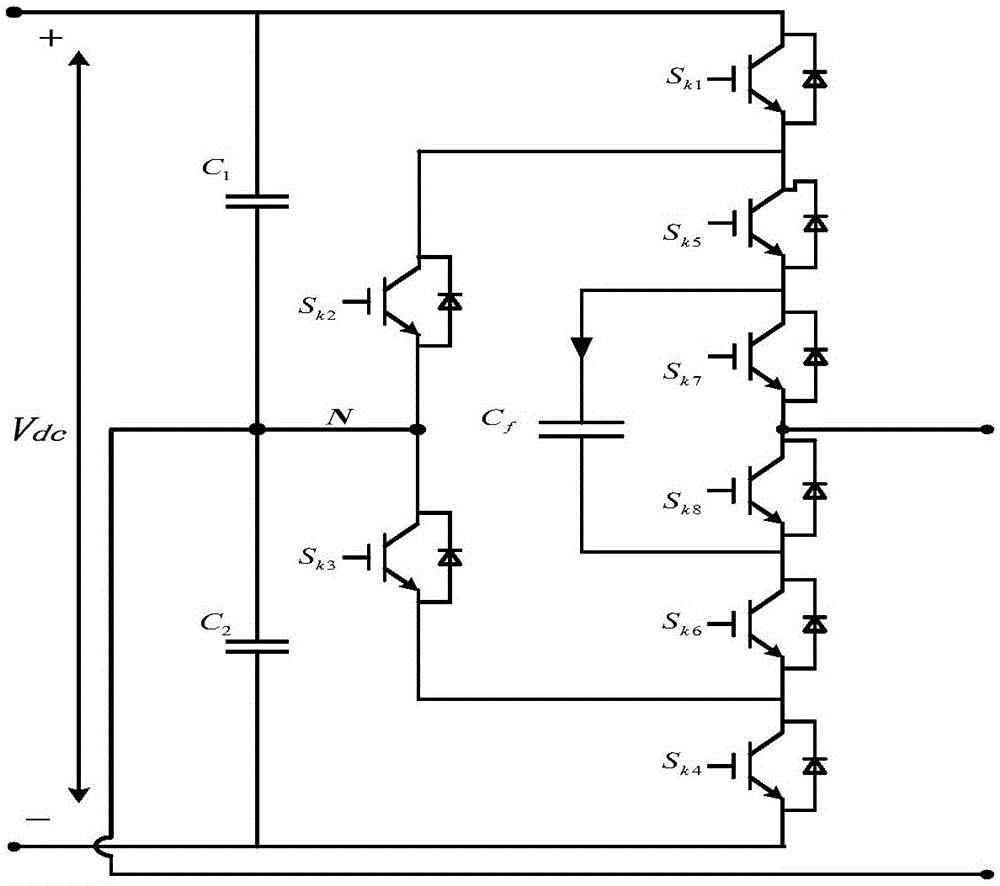

[0075] The circuit topology of each phase of the three-phase five-level inverter involved in the present invention is the same, and its single-phase topology diagram is as follows figure 2 shown. The total DC bus voltage is V dc , the DC side is provided with two capacitors C connected in series 1 and capacitance C 2 , capacitance C 1 The positive pole is connected to the positive pole of the inverter input, and the capacitor C 1 Negative electrode and capacitor C 2 The positive connection point is defined as the midpoint of the inverter; it contains 8 switching tubes, namely the switching tube S ki , i=1,2,3...8,k=a,b,c, where k represents the three-phase circuit of the inverter, that is, phase a, phase b, phase c; switch tube S k1 , switch tube S k5 , switch tube S k7 , switch tube S k8 , switch tube S k6 , switch tube S k4 in series, the switching tube S k1 The emitter is connected to the switch tube S k5 collector, switching tube S k5 The emitter is connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com