VLSI (Very Large Scale Integration) formal verification platform and method

A large-scale integrated circuit and formal verification technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of large time overhead, multiple chip levels, and large differences in modules, so as to reduce the reading time the effect of consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

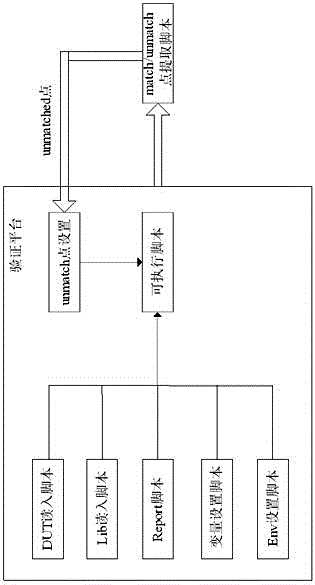

[0027] Such as figure 1 As shown, a VLSI formalized verification platform for VLSI, the verification platform includes components: variable setting script, Lib read-in script, DUT read-in script, Env setting script, Report setting script, and the verification platform also includes The match / unmatch point extraction script that processes the output results of the verification platform, once the detection verification fails, there is an unmatch point, which can automate the iterative work, among which:

[0028] Variable setting script, which uniformly sets macro variables such as Lib / DUT read-in path, result output path, and top-level name to be tested. It is responsible for setting variables such as the top-level name, source path, report path, and library path of each DUT. It has a full platform Versatility;

[0029] Lib read-in scripts, manage the reading of standard cell libraries and various IPs (storage IP, PAD IP and other IP libraries), manage each module Lib separatel...

Embodiment 2

[0038] On the basis of Embodiment 1, the Env environment setting script described in this embodiment can be shared by all platforms.

Embodiment 3

[0040] On the basis of Embodiment 1 or 2, the match / unmatch point extraction script described in this embodiment is created using perl. There may be hundreds, thousands, or even more unmatch points in the verification, and the platform output format cannot be directly read into the platform environment. Therefore, using the powerful text processing capability of perl, a match / unmatch point extraction script is created. Once There is an unmatch point if the detection verification does not pass, which can automate the iterative work.

[0041] Perl, a feature-rich computer programming language that runs on more than 100 computer platforms and is applicable to a wide range of applications, from mainframes to portable devices, from rapid prototyping to massively scalable development; generally referred to as "Practical Report Extraction Language" "(Practical Extraction and Report Language), you may also see "perl", all letters are lowercase. Generally, "Perl", with a capital P, re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com